# Challenges in Nanoscale Devices and Breakthroughs

### Woo Young Choi

#### Dept. of Electronic Engineering Sogang University

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

# IC History

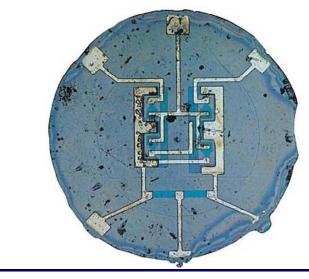

| *  | 1947 The first transistor (Bell Telephone Laboratories)                                          |

|----|--------------------------------------------------------------------------------------------------|

| *  | 1958 The first integrated circuit available as a monolithic chip (flip-flop) (Texas Instruments) |

| *  | <b>1959 The first bipolar planar transistor (Fairchild)</b>                                      |

| ** | 1960 The first MOSFET (Bell Telephone Laboratories)                                              |

| *  | 1965 The first op-amp                                                                            |

| *  | 1971 The first 4bit microprocessor (Intel 4004)                                                  |

| *  | 1972 The first 8bit microprocessor (Intel 8008)                                                  |

\*1981 The first IBM PC

| TIDL | 4/50 | Dept. of Electronic Eng., Sogang University |

|------|------|---------------------------------------------|

|------|------|---------------------------------------------|

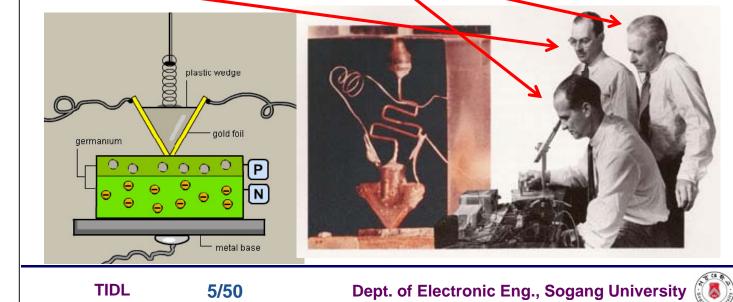

# **Genesis of Transistors**

They received the Nobel Prize in Physics in 1956!

Affiliations: Bell Telephone Laboratories

Inventors: William Shockley (leader), John Bardeen(theorist), Walter Brattain (experimenter)

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

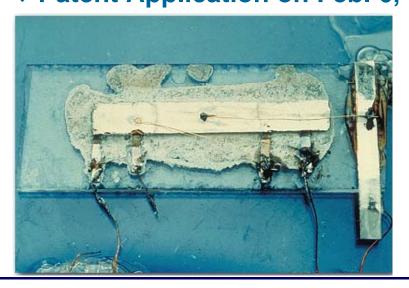

### **First IC**

#### When: 1958

- Affiliations: Texas Instruments

- Inventors: Jack Kilby

He also received the Nobel Prize in Physics in 2000! Patent Application on Feb. 6, 1959 (Rejected)

6/50

8/50

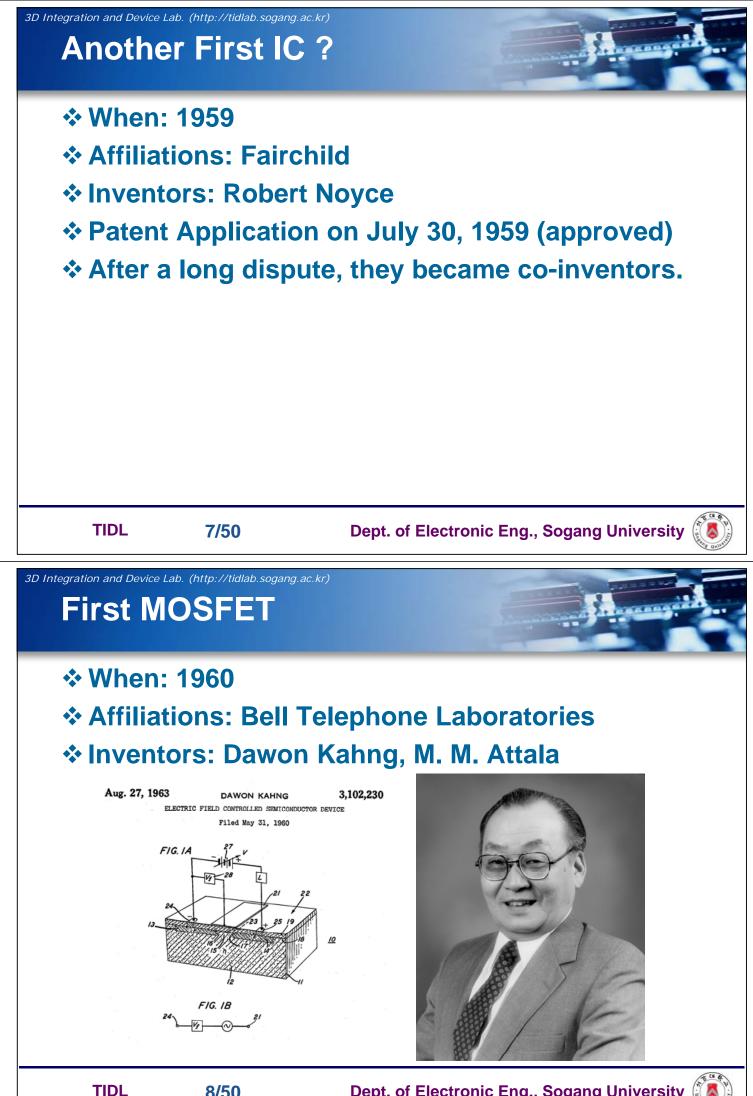

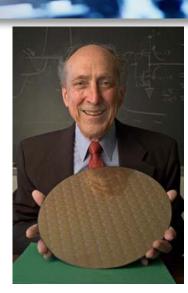

# **First Silicon IC**

#### \* When: 1961

Affiliations: Fairchild

He is one of the Intel's cofounders!

- Inventors: Robert Noyce

- \* The first commercially available IC.

TIDL

9/50

Dept. of Electronic Eng., Sogang University

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

# Fairchild (or Traitorous) Eight

- William Shockley, who left Bell Labs in 1954 to start its own company in Palo Alto, CA. --> Silicon Valley

- Young people, such as Robert Noyce, joined Shockley Company.

- The "traitorous eight" including Robert Noyce, as Shockley came to call them, set up in 1957 Fairchild

- Fairchild: in 1959 new planar technology

William Shockley's employees drink a toast to him on the day in 1956 when he was awarded the Nobel Prize in Physics for inventing the transistor. Eight of the crew shown here, went off on their own the next year and founded Fairchild Semiconductor Corporation.

From left: Gordon Moore, Sheldon Roberts, Eugene Kleiner, Robert Noyce, Victor Grinich, Julius Blank, Jean Hoerni, and Jay Last.

10/50

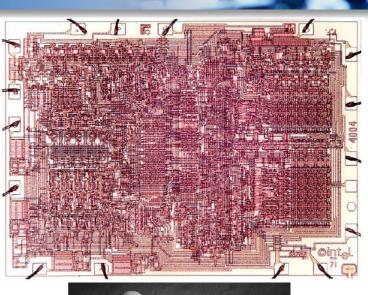

# **First Microprocessor**

- \* When: 1971

- Affiliations: Intel

- \* Name: Intel 4004

### 2,300 Transistors

The Intel 4004 was originally designed for use in a Busicom scientific calculator (Japan), but Intel engineers realized the design of the chip afforded multi-purpose use - thus the microprocessor was born.

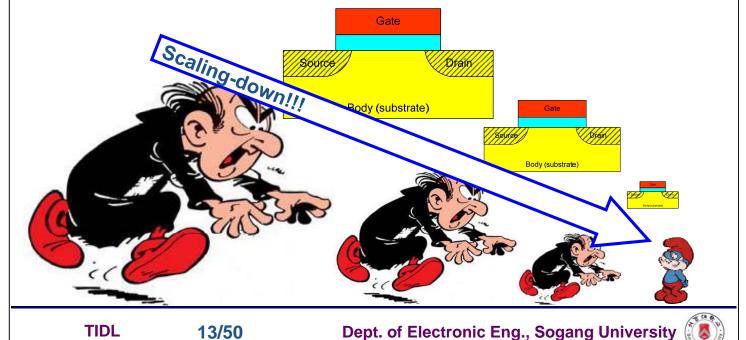

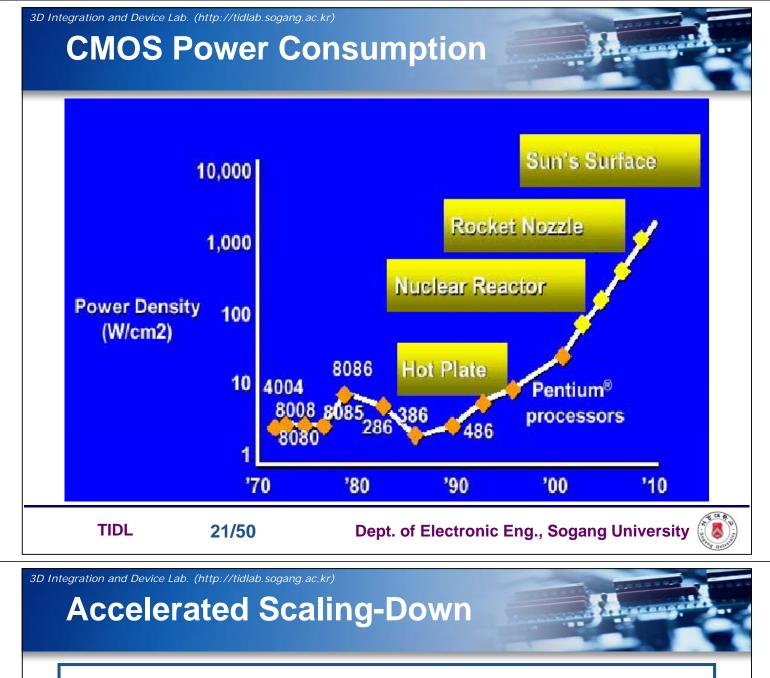

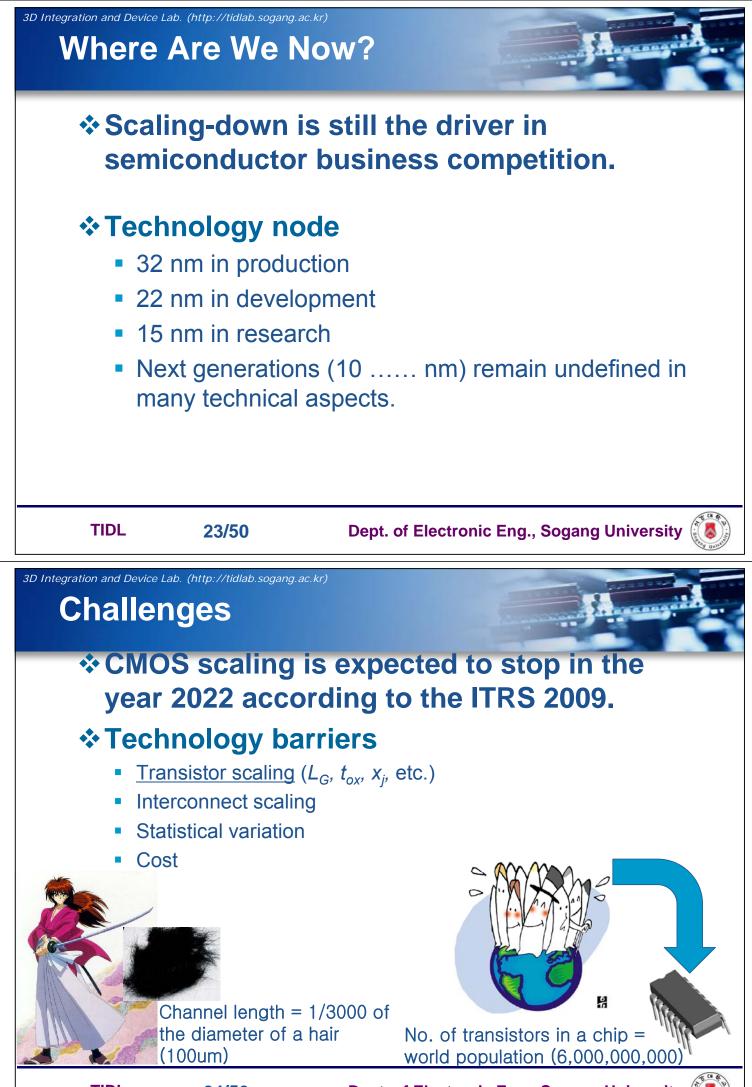

# CMOS Scaling (1)

### Definition of MOSFET scaling(-down)

The reduction of lateral and vertical geometric dimensions of MOSFETs

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

# **CMOS Scaling (2)**

### Difference between MOSFETs and Gagamel

- Gagamel: the smaller, the weaker. No advantages over Smurfs.

- MOSFET: the smaller, the stronger!

#### What's the meaning of "stronger"?

- More devices at the same area (cheaper price per device)

- Higher performance (higher speed)

- Lower power consumption

That's why semiconductor manufacturers are desperate to scale down devices.

#### How to Scale Down

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

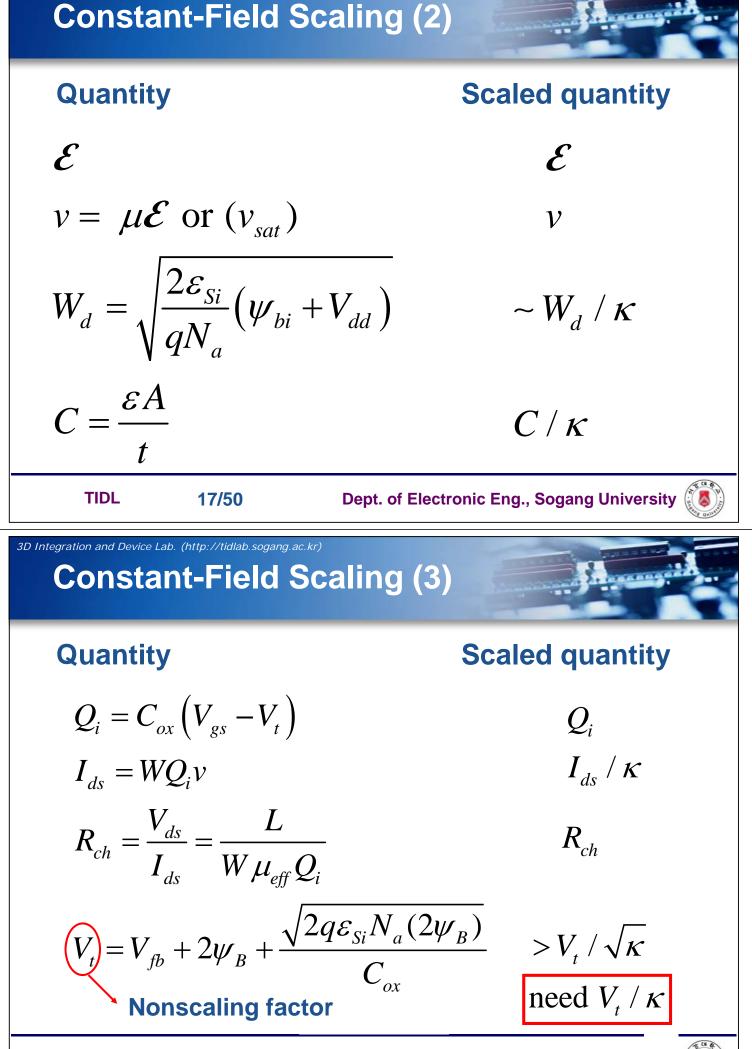

# Constant-field scaling

- Proposed by Robert Dennard *et al.* (1974)

- Ideal scaling-down way

- Scaling the device voltages and the device dimensions (both horizontal and vertical) by the same factor(κ), so that the electric field remains unchanged.

# Constant-voltage scaling Generalized scaling

15/50

Constant-Field Scaling (1)

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

**Objective:**

TIDL

Maintain a constant electric field as dimensions are scaled down.

L, W,

$$t_{ox}$$

,  $x_j \rightarrow L/\kappa$ ,  $W/\kappa$ ,  $t_{ox}/\kappa$ ,  $x_j/\kappa$

$$N_a \to \kappa N_a$$

$$V_{dd} \rightarrow V_{dd} \ / \kappa$$

# **Constant-Field Scaling (2)**

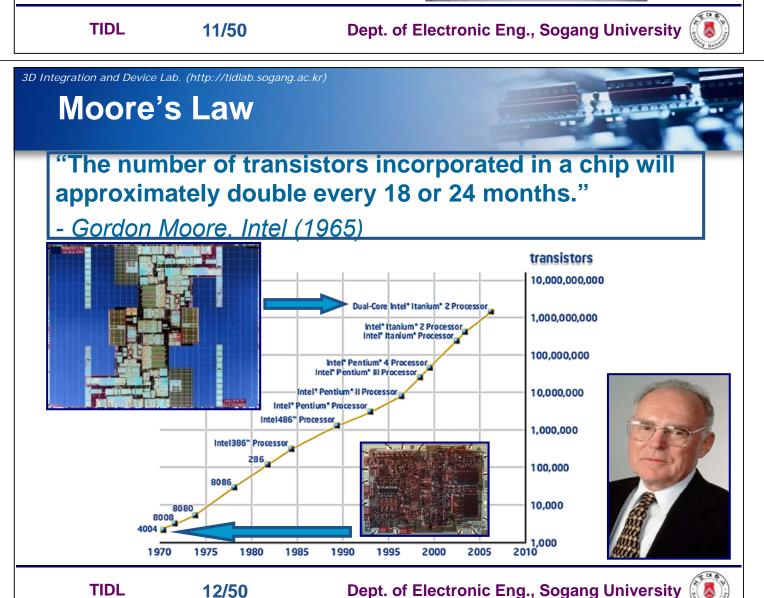

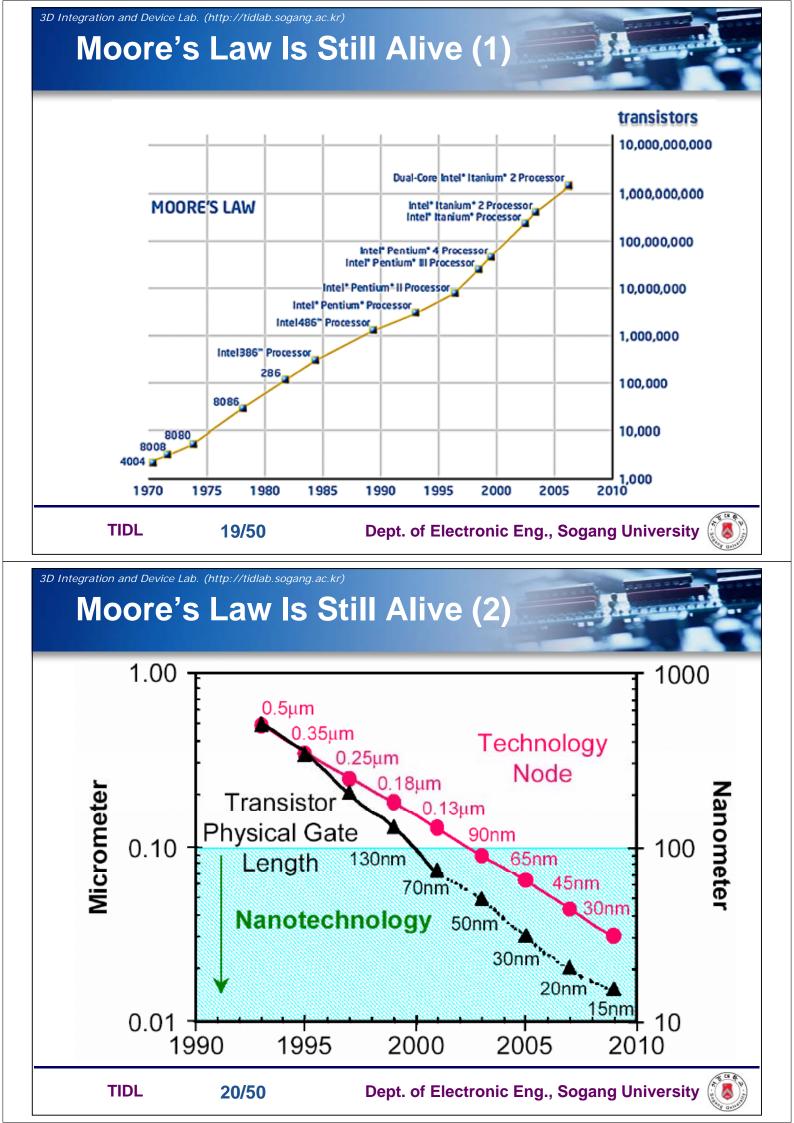

"The number of transistors incorporated in a chip will approximately double every 18 or 24 months."

- Gordon Moore, Intel (1965)

"The paradigm shift in the memory industry requires a new memory growth model: a twofold increase per year in memory density."

- Chang-Gyu Hwang, Samsung (2002)

TIDL

TIDL

24/50

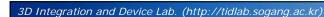

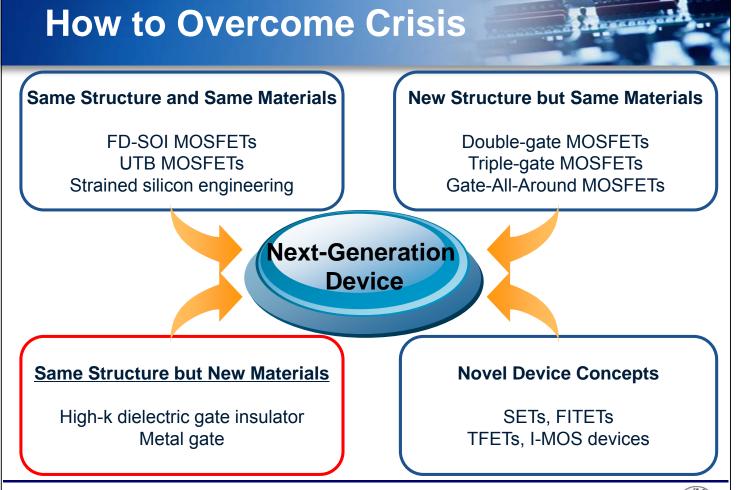

# **Conventional Approach (1)**

#### 3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

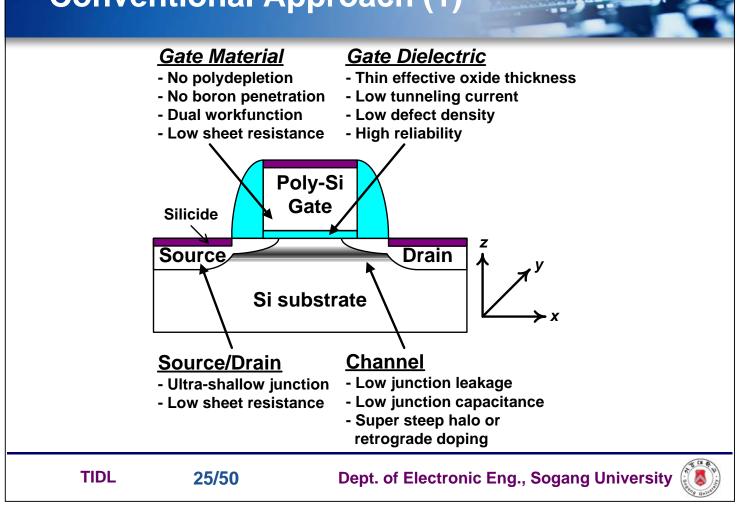

# **Conventional Approach (2)**

## Limitations

- Gate length (L<sub>G</sub>) has scaled thanks to the scaling of gate oxide thickness (t<sub>ox</sub>), source/drain junction depth (x<sub>j</sub>), substrate doping concentration (N<sub>sub</sub>), and operating voltage (V<sub>DD</sub>).

- N<sub>sub</sub> increases at the cost of channel mobility, which leads to performance degradation.

- Nevertheless, performance is enhanced by lowering  $V_{\text{TH}}$ , thinning  $t_{\text{ox}}$ , slowing  $V_{\text{DD}}$  scaling.

- So, performance improvement and static power consumption are inevitable.

TIDL

28/50

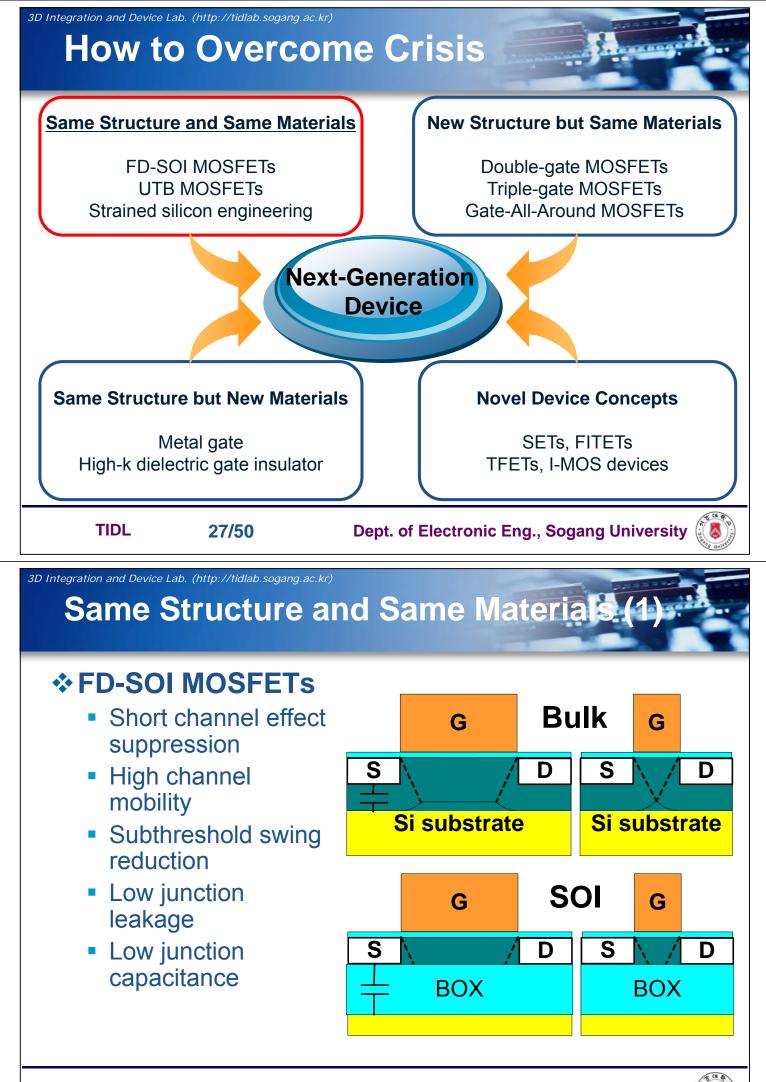

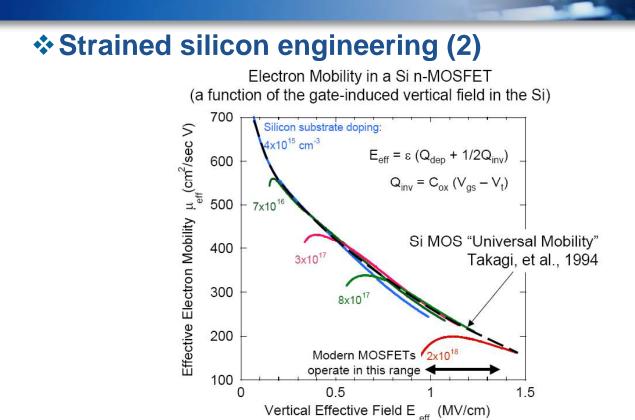

Same Structure and Same Materials (2)

### Strained silicon engineering (1)

- To minimize gate delay (increase speed), drain current should be increased.

- Increase of drain current

- $L_G$  reduction

- t<sub>ox</sub> reduction

- Carrier mobility enhancement no side effect if possible

$$I_{DS,sat} = \mu_{eff} \frac{\mathcal{E}_{ox}}{t_{ox}} \frac{W}{L_G} \frac{(V_G - V_T)^2}{2}$$

TIDL

29/50

Dept. of Electronic Eng., Sogang University

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

# Same Structure and Same Materials (3)

Same Structure and Same Materials (4)

# Strained silicon engineering (3)

Desired types of uniaxial stress

|            | nMOSFET                                  | pMOSFET     |  |

|------------|------------------------------------------|-------------|--|

| X          | Tensile                                  | Compressive |  |

| Y          | Tensile                                  | Tensile     |  |

| Z          | Compressive                              | Tensile     |  |

| TIDL 31/50 | Dept. of Electronic Eng., Sogang Univers |             |  |

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

TIDL

# Same Structure but New Materials (1)

# High-k dielectric (1)

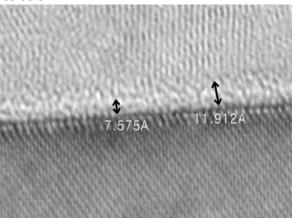

- The success of CMOS technology is greatly owed to the excellent properties of SiO<sub>2</sub>.

- Properties of SiO<sub>2</sub>

- Electrically neutralized Interface states

- Easy to grow on silicon substrate

- · Easy to integrate in a process

- High energy bandgap

- Stability

- Scalability

However, gate oxide thickness has reached its limit.

TIDL

33/50

Dept. of Electronic Eng., Sogang University

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

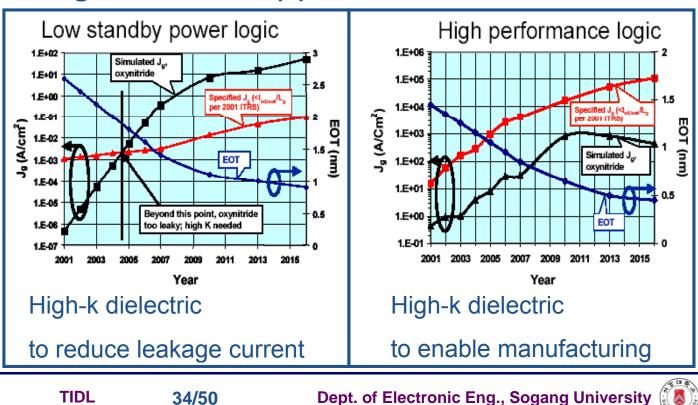

Same Structure but New Materials (2)

# High-k dielectric (2)

# Same Structure but New Materials (3)

| * |                                                            | constant<br>ompatibility<br>y<br>grown by<br>Vapor Deposition)<br>Vapor Deposition) |                         |                |

|---|------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------|----------------|

|   | TIDL 35/50                                                 | Dept. of Electronic                                                                 | Eng., Sogang University | B CH CH PP - A |

|   | ation and Device Lab. (http://tidlab.soga<br>Same Structur | e but New Ma                                                                        | terials (4)             |                |

| * | High-k dielectri Candidates                                | c (4)                                                                               |                         |                |

|   |                                                            | Dielectric const.                                                                   | Bandgap (eV)            |                |

|   | HfO <sub>2</sub>                                           | 24                                                                                  | 5.7                     |                |

| I | Al <sub>2</sub> O <sub>3</sub>                             | 9                                                                                   | 8.7                     |                |

|   | Ta <sub>2</sub> O <sub>5</sub>                             | 26                                                                                  | 4.5                     |                |

|   | ZrO2                                                       | 25                                                                                  | 7.8                     |                |

|   |                                                            |                                                                                     |                         |                |

TIDL36/50Dept. of Electronic Eng., Sogang University

8

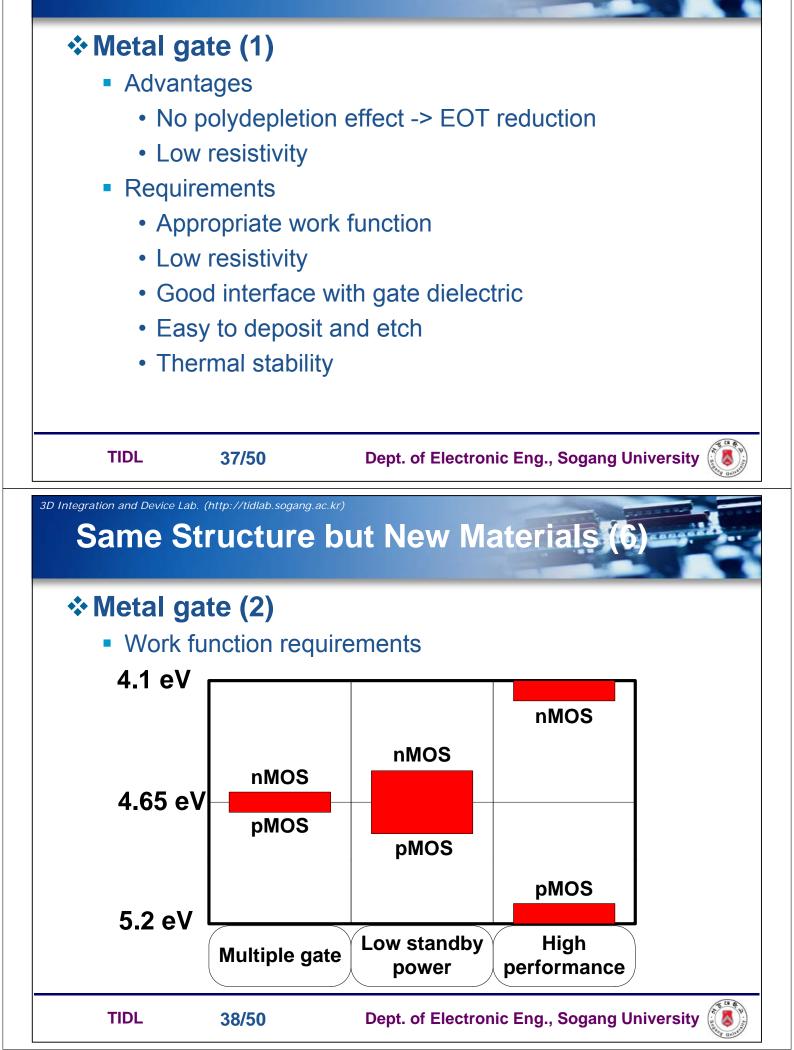

# Same Structure but New Materials (5)

TIDL

42/50

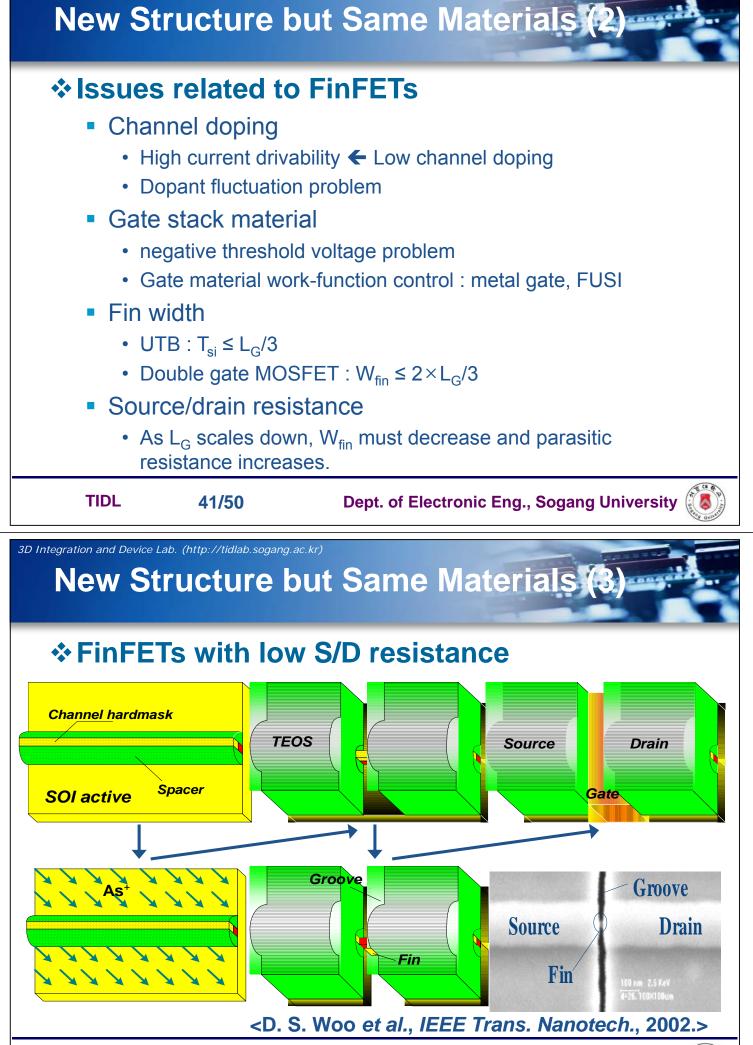

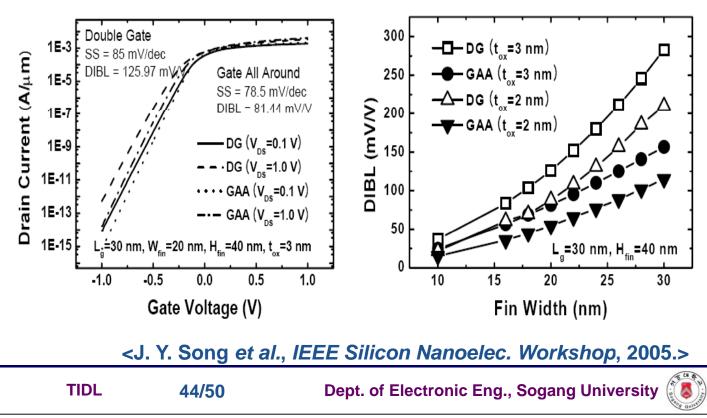

New Structure but Same Materials (4)

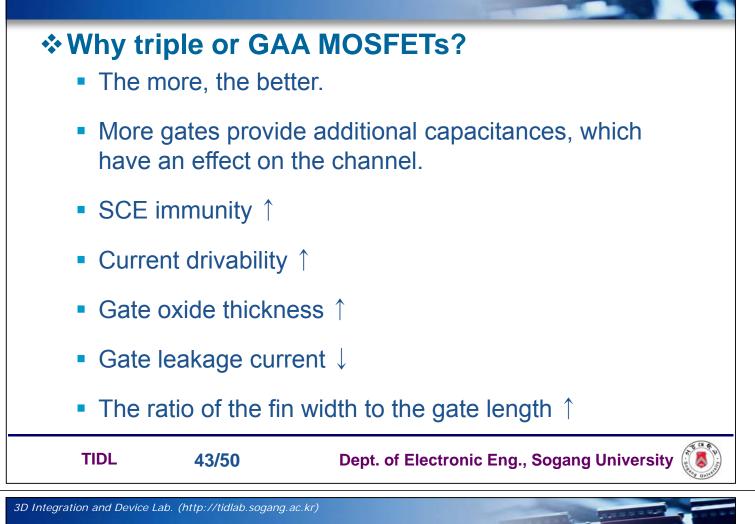

New Structure but Same Materials (5)

# Double-gate vs. GAA MOSFETs

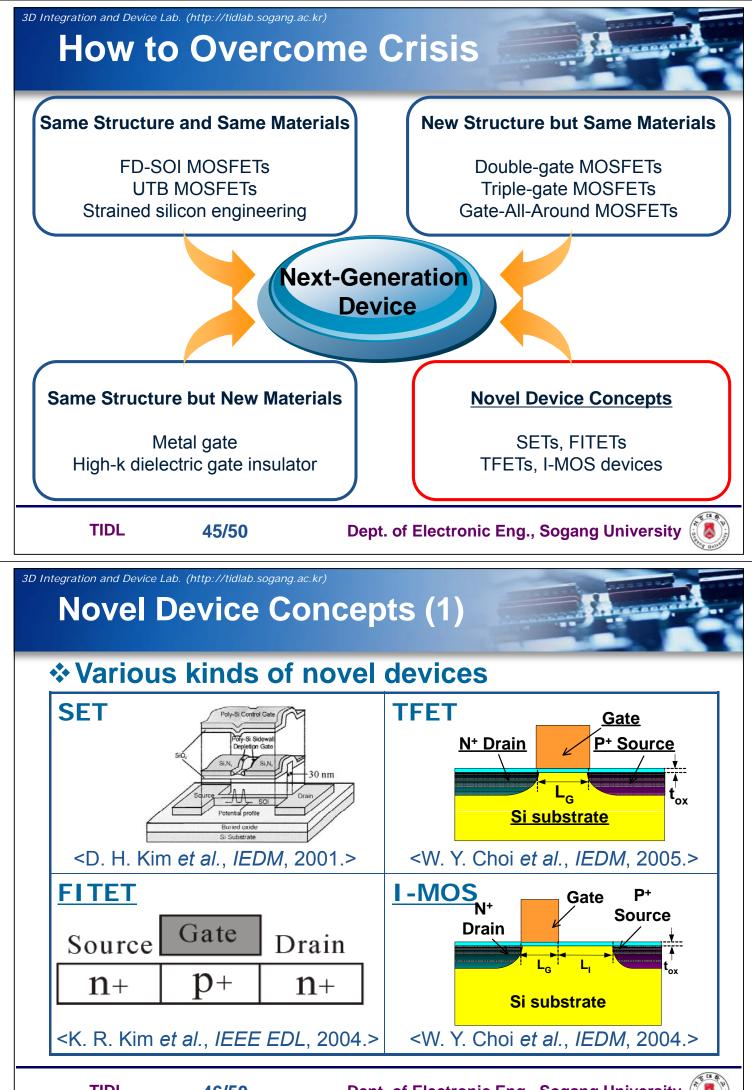

# **Novel Device Concepts (5)**

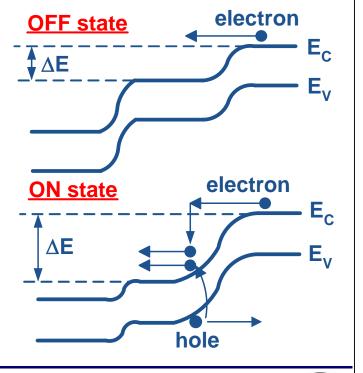

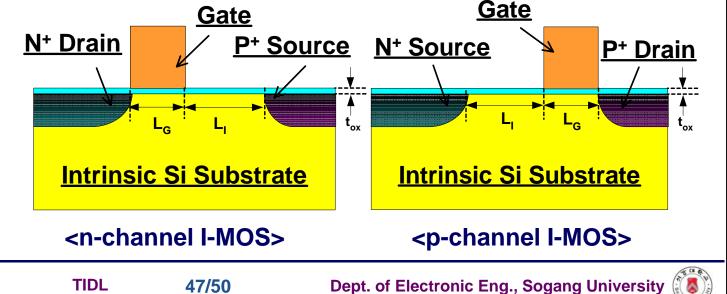

# **♦ I-MOS (1)**

- It uses modulation of avalanche breakdown voltage of a gated p-i-n diode.

- Subthreshold swing less than 60 mV/dec at room temp.

3D Integration and Device Lab. (http://tidlab.sogang.ac.kr)

# **Novel Device Concepts (6)**

# **\*I-MOS (2)** – basic operation principle

- OFF state (V<sub>G</sub> < V<sub>TH</sub>): The energy between the channel and the source is not enough to induce avalanche breakdown.

- ON state (V<sub>G</sub> > V<sub>TH</sub>): The energy between the channel and the source is enough to induce avalanche breakdown.