# **Project for Electronic Circuits I**

Prof. Woo-Young Choi TA: Minkyu Kim Dec. 8, 2015

- Deadline : 10:00 am on Dec. 23, 2015. Penalties for late hand-in.

#### - MOS PSpice parameters

Use Level 7 PSpice parameters for 0.25µm CMOS process. The course homepage has PSpice 9.1 student version, level 7 PSpice parameters as well as PSpice basic manual.

#### - Design rules

- 1. VDD = 2.5V

- 2. 0.25 $\mu$ m  $\leq$  length of gate  $\leq$  2 $\mu$ m

- 3. 0.25 $\mu$ m  $\leq$  width of gate  $\leq$  100 $\mu$ m

- 4. Body of pMOS must be connected to VDD

- 5. Body of nMOS must be connected to GND

#### - Goal

You are expected to design an MOSFET amplifier satisfying given specifications. The project is divided into two parts (MOSFET small-signal parameter extraction and amplifier design) so that you can build up your design.

Your design will be evaluated based on following criteria:

- 1. How well you satisfy the specifications.

- 2. How large gain you achieve.

- 3. How well you explain your design flow in your report.

## I. nMOS & pMOS small-signal parameter extraction [20]

Design nMOS & pMOS transistors that satisfy the given design goals.

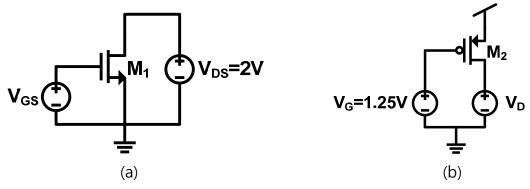

Fig1. Schematic of nMOS & pMOS

$V_{\text{DS}}$  is 2V for nMOS and  $V_{\text{G}}$  is 1.25V for pMOS.

| Design Goals                                       |        |  |

|----------------------------------------------------|--------|--|

| Parameter                                          | Value  |  |

| Maximum transconductance(g <sub>m</sub> ) for nMOS | >3mS   |  |

| r <sub>o</sub> for pMOS                            | >185kΩ |  |

You should include the following in the report.

(1) How you achieved design goals.

(2) Simulation results

-Circuit Schematics

- Simulated I-V curves with which you calculated small-signal parameters

(3) Discussion on the difference between simple models we learned in the class and the simulated results?

## II. Amplifier [50]

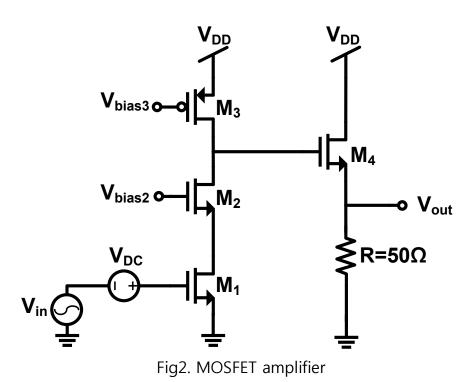

Design the following amplifier which satisfies the given design goals.

Assume  $V_{in}\,is\,\,1\text{KHz}$  sinusoidal with  $5mV_{pp}\,.$

| Design Goals                                    |                      |  |

|-------------------------------------------------|----------------------|--|

| Parameter                                       | Value                |  |

| Available output swing                          | >0.8 V <sub>pp</sub> |  |

| $ A_{v}  = \left \frac{v_{out}}{v_{in}}\right $ | >40dB                |  |

| Power consumption                               | <35mW                |  |

You should include the following in the report.

(1) How you achieved design goals and optimized your gain.

(2) Simulation Results

-Schematics

-DC sweep simulation results for output swing

-Transient simulation results for gain calculation

(3) Discussion on the difference between simple models we learned in the class and the simulated results?

#### III. Design Report [30]

Write a design report in which you clearly explain how you come up with your transistor W/L values, what you have achieved for each design goal, simulation results. All your design results should be summarized in Design Summary Sheet. Place the Design Summary Sheet right after the cover page of your report.

\*\* Maximum Report pages : 10 (Not including Cover, Design Summary Sheet)

# **Design Summary Sheet**

Name :

Student ID No. :

## < nMOS & pMOS small-signal parameter extraction >

| (W/L)1                 |  |

|------------------------|--|

| (W/L) <sub>2</sub>     |  |

| Maximum g <sub>m</sub> |  |

| r <sub>o</sub>         |  |

## < Amplifier >

| (W/L)1                 |  |

|------------------------|--|

| (W/L) <sub>2</sub>     |  |

| (W/L) <sub>3</sub>     |  |

| (W/L) <sub>4</sub>     |  |

| V <sub>DC</sub>        |  |

| V <sub>bias2</sub>     |  |

| V <sub>bias3</sub>     |  |

| Available output swing |  |

| A <sub>v</sub>         |  |

| Power consumption      |  |