High-Speed Circuits & Systems Lab.

Dept. of Electrical and Electronic Engineering

Yonsei University

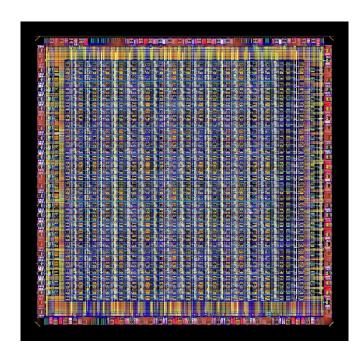

Process : DBH 90nm CIS (BSI)Area : 4,460um × 4,350um

Design : SPAD AFEs

<TOP View>

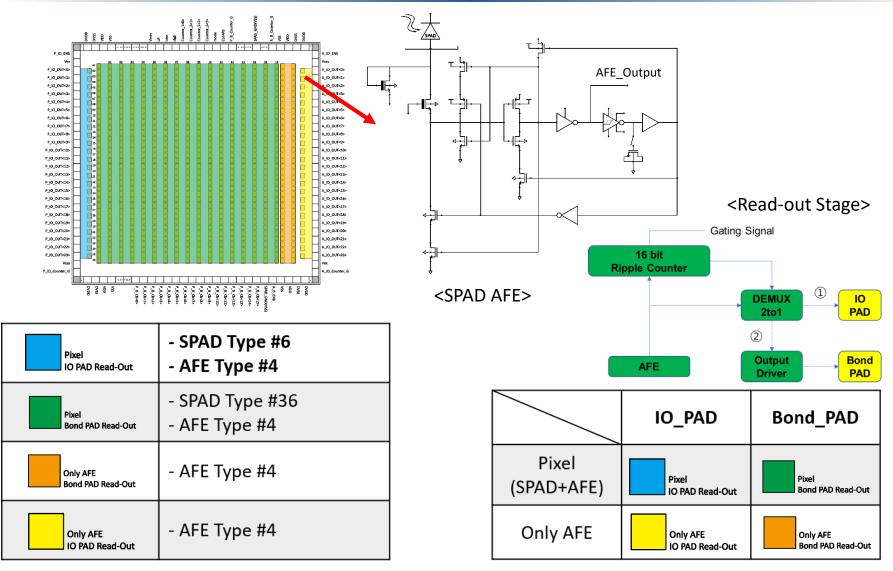

#### - Purpose

- 1) Detect sub-ns output pulse.

- 2) Verify differences about output characteristic between 'I/O Pad' and 'Bond Pad'

- 3) Designed SPAD verification.

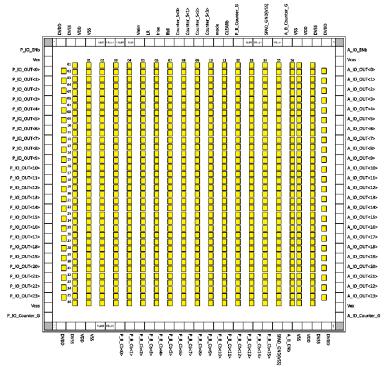

<TOP Concept View>

Process: DBH 110nm CIS (BSI)

Area: 1,490um × 1,490um

Design: SPAD AFEs & Device

mm 關北縣

<TOP View>

#### Purpose

- 1) Detect sub-ns output pulse.

- 2) Verify differences about output characteristic between 'I/O Pad' and 'Bond Pad'

- 3) Designed SPAD verification.

<SPAD AFE & Read-out>

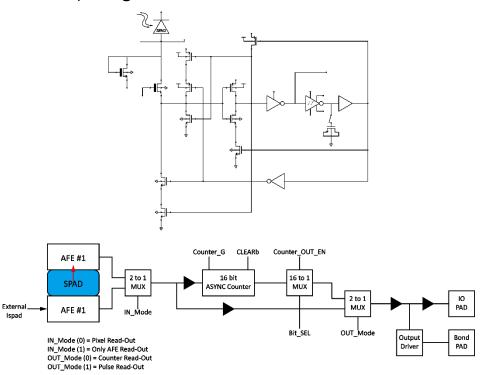

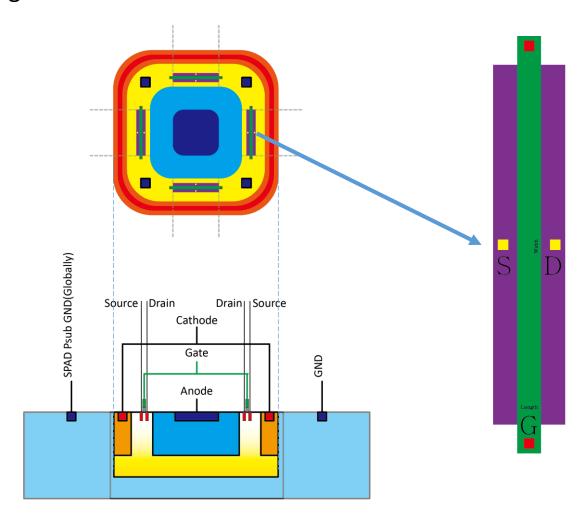

### <SPAD Integrated with MOSFET>

# **Future Plan**

- 1. Imaging System Setup (w/JH Kim)

- 2. SPAD Device Measurement & Thesis Writing

- 3. Research & Design Large SPAD Array using Verified AFE