> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

# 3D-Stacked Back-Illuminated Single-Photon Avalanche Diode Pixel With a Pitch of 3.5 $\mu\text{m}$

Eunsung Park, Hyo-Sung Park, Hyun-Seung Choi, Woo-Young Choi, *Member, IEEE*,

and Myung-Jae Lee, *Member, IEEE*

**Abstract**—Single-photon avalanche diode (SPAD) pixel scaling is essential to meet the increasing demands for high-resolution, compact, and power-efficient time-of-flight (ToF) sensing. In particular, the 3D-stacked approach enables aggressive pixel scaling by separating the SPAD and readout circuits into different wafers, thus maximizing the fill factor while minimizing the pixel pitch. However, pixel miniaturization often leads to degraded SPAD performance due to the premature edge breakdown (PEB) and the reduced number of photon-generated carriers that go through the avalanche multiplication region. In this work, we overcome these challenges by optimizing the doping profile to enhance the carrier collection in the device. We present a detailed analysis of the optimization progress by evaluating breakdown voltage ( $V_B$ ), dark count rate (DCR), and photon detection probability (PDP), highlighting the trade-offs and recovery achieved through successive doping refinements. The optimized device achieves a PDP of 37% and a timing jitter of 85 ps at 940 nm. Compared to prior 3D-stacked back-illuminated (BI) SPADs, our work exhibits one of the smallest pixel pitches to date, yet retains competitive PDP and jitter characteristics. This combination of aggressive scaling and robust performance positions the proposed SPAD as a promising solution for LiDAR, 3D imaging, and future wearable sensing systems.

**Index Terms**—3D imaging, 3D photonics, 3D-stacked SPAD sensor, back-illuminated SPAD, LiDAR, photon detection probability (PDP), pixel pitch, pixel scaling, resolution, single-photon avalanche diode (SPAD), timing jitter.

## I. INTRODUCTION

SiNGLE-PHOTON avalanche diodes (SPADs) have emerged as a key enabler in a wide range of modern photonic applications, including light detection and

Manuscript received 31 August 2025; revised; accepted. This work was supported by the Yonsei University Research Fund of 2024 (2024-22-0504), the Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Ministry of Science and ICT (MSIT, Korea) (RS-2025-02218723), and the Technology development Program funded by the Ministry of SMEs and Startups (MSS, Korea) (00507002). (Eunsung Park and Hyo-Sung Park contributed equally to this work.) (Corresponding author: Woo-Young Choi, Myung-Jae Lee.)

E. Park, H.-S. Park, and W.-Y. Choi are with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea.

H.-S. Choi is with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea, and also with Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea.

M.-J. Lee is with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea, and also with TruPixel, Inc., Daejeon 34138, South Korea (e-mail: mj.lee@yonsei.ac.kr).

Color versions of one or more of the figures in this article are available online at <http://ieeexplore.ieee.org>

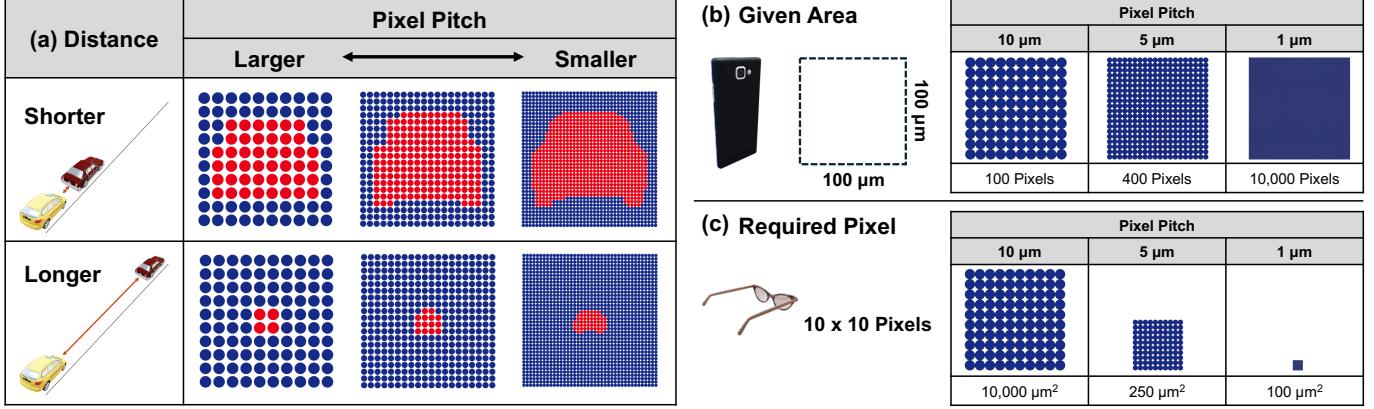

ranging (LiDAR), fluorescence lifetime imaging (FLIM), time-of-flight (ToF) ranging, and quantum information processing [1]–[4]. To further expand their applicability, there is an increasing demand for higher-resolution SPAD arrays with smaller pixel pitches. Pixel miniaturization not only improves the spatial resolution in depth sensing but also allows more pixels to be integrated into constrained chip areas—an essential feature in both automotive and mobile/wearable applications. Fig. 1 illustrates the impact of pixel scaling in two scenarios. As shown in Fig. 1(a), smaller pixel pitches lead to more accurate shape recognition across a wide range of distances—an essential feature for automotive LiDAR systems, where distinguishing surrounding objects is directly linked to safety. Even with large pixels, SPAD arrays can reconstruct nearby objects, but smaller pixel pitches enable more detailed shapes—especially at longer distances, where they preserve recognizable forms critical for object classification and navigation in autonomous systems [5]. In mobile applications such as AR/VR headsets, smartphones, and wearable sensors, where size and power constraints are stringent, pixel scaling enables substantial advantages in integration density [6]. Fig. 1(b) shows that reducing the pixel pitch from 10  $\mu\text{m}$  to 1  $\mu\text{m}$  increases the pixels from 100 to 10,000 within a fixed  $100 \times 100 \mu\text{m}^2$  area. This scaling enhances depth resolution in compact 3D sensors without enlarging the sensor. Fig. 1(c) further shows that, for a fixed pixel count (e.g.,  $10 \times 10$ ), pixel miniaturization dramatically reduces the required area—down to 100  $\mu\text{m}^2$  at 1  $\mu\text{m}$  pitch—making integration feasible in space-constrained modules such as AR and wearable devices.

Despite these benefits, scaling SPAD pixels presents several challenges in conventional front-illuminated (FI) and even back-illuminated (BI) CMOS processes. FI SPADs, while structurally simple and fully CMOS-compatible, suffer from limited photon detection probability (PDP), particularly in the near-infrared (NIR) wavelengths commonly used in LiDAR systems [7]. This is primarily due to optical blockage by front-side metal layers and shallow absorption depth at longer wavelengths, which restricts effective photon absorption. Moreover, both the SPAD and its readout circuitry must share the same silicon plane, which limits fill factor and constrains pixel pitch scaling due to routing complexity and area overhead. To overcome these limitations, BI SPADs relocate the photon entry point to the back-side of the wafer, thereby avoiding metal-induced shading and improving PDP [8]. However, despite these optical advantages, BI architectures still retain a critical bottleneck: the SPAD and its associated circuits must coexist within the same layer, limiting

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 1. Impact of SPAD pixel pitches on spatial resolution and integration density for LiDAR and mobile/wearable applications.

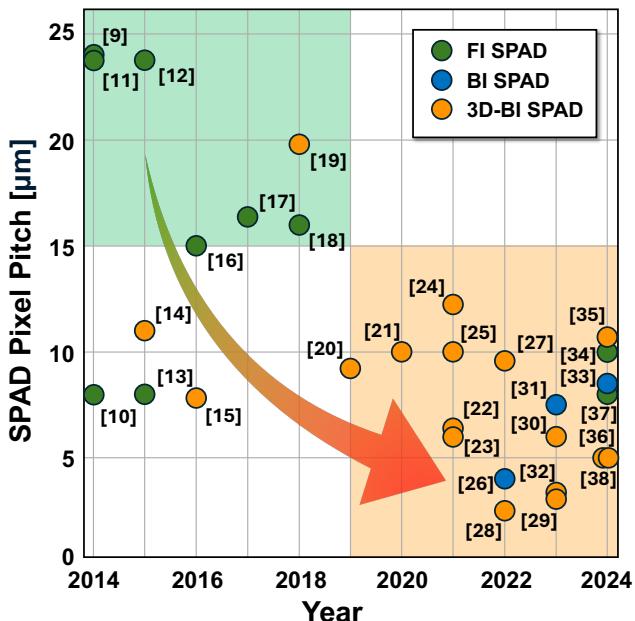

how tightly pixels can be packed. These architectural transitions and their impact on pixel scaling are illustrated in Fig. 2, which summarizes the evolution of SPAD pixel pitch over the past decade [9]–[38]. Early FI SPADs, prevalent before 2018, maintained relatively large pixel sizes above 15  $\mu\text{m}$ . The adoption of BI structures subsequently enabled further scaling down to  $\sim 10 \mu\text{m}$ . However, as shown in the orange-shaded region, most of the recent progress—particularly pitches below 5  $\mu\text{m}$ —has been achieved through the 3D-stacked approach, which decouples the SPAD and readout layers. To leverage this architectural trend, 3D-stacked SPADs have emerged as a promising approach. By vertically separating the SPAD from the readout circuit and connecting them through hybrid bonding, 3D integration enables more aggressive pitch scaling while retaining full per-pixel functionality. It also facilitates the use of optimized doping profiles and layer thicknesses in each tier, decoupling the conflicting design requirements between detection and readout.

While 3D-stacked architectures offer a clear path toward aggressive pixel miniaturization, fundamental structural

constraints of SPADs still impose significant challenges. Key elements of the SPAD structure—such as the p-n junction, guard ring (GR), and bias ring (BR)—are essential for operating the SPAD, yet they occupy a minimum area that becomes increasingly difficult to accommodate as the pixel-pitch shrinks. As a result, further miniaturization can compromise the SPAD's performance, most notably by reducing the photon detection probability (PDP). This degradation is primarily attributed to a smaller carrier collection volume and non-uniform avalanche multiplication near the edge of the p-n junction. However, the flexibility offered by the 3D stacking enables independent optimization of the top-tier SPAD layers. In particular, the doping profile of the SPAD can be finely tuned to mitigate PDP degradation while maintaining compact pixel dimensions. Preliminary results on doping-profile optimization were presented in Ref. [39]. In this paper, we provide comprehensive measurement results and detailed analysis of the doping optimization process integrated into a 3D-stacked SPAD platform. The remainder of this paper is organized as follows. Section II outlines the impact of pixel miniaturization on SPAD performance, particularly the degradation in PDP. Section III presents the optimization of the doping profile to restore PDP while maintaining compact dimensions. Section IV provides comprehensive electrical and optical characterization results of the optimized device. Section V benchmarks the proposed SPAD against state-of-the-art SPADs and concludes the paper.

## II. PIXEL SHRINKING IN 3D-BI CIS TECHNOLOGY

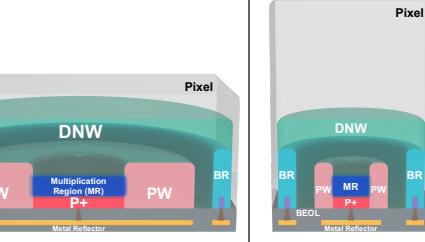

To enable ultra-high-density SPAD arrays, we explored aggressive pixel miniaturization using a 40 nm 3D-stacked BI CIS process. This advanced technology provides favorable design margins—such as tighter metal routing, finer lithography, and deeper well structures—that facilitate aggressive scaling while preserving SPAD functionality. Fig. 3 compares the previously reported SPAD from Ref. [33] and the newly scaled version in this study. The pixel pitch is reduced from 8 to 3.5  $\mu\text{m}$  by employing cathode sharing between adjacent SPADs. While the reference SPAD adopts a conventional BI technology, this work leverages a 3D-stacked BI technology to enable tighter vertical integration. In

Fig. 2. Pixel-pitch evolution of SPADs over the past decade.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

|                      | Ref. [33]         | This Work                                                                         |

|----------------------|-------------------|-----------------------------------------------------------------------------------|

| Pitch                | 8 $\mu\text{m}$   | 3.5 $\mu\text{m}$                                                                 |

| Silicon Thickness    | 4 $\mu\text{m}$   | 7 $\mu\text{m}$                                                                   |

| PN Junction          | 2.5 $\mu\text{m}$ | 1 $\mu\text{m}$                                                                   |

| Simplified X-section |                   |  |

Fig. 3. Comparison of SPADs with pitches of 8 and 3.5  $\mu\text{m}$ .

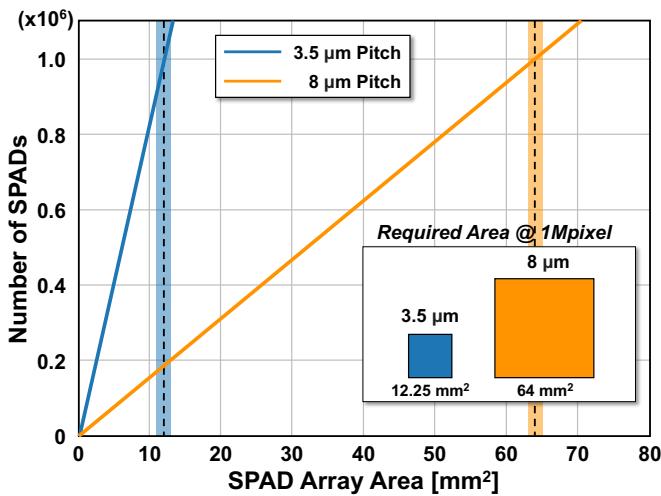

Fig. 4. Comparison of SPAD array scaling with different pixel pitches.

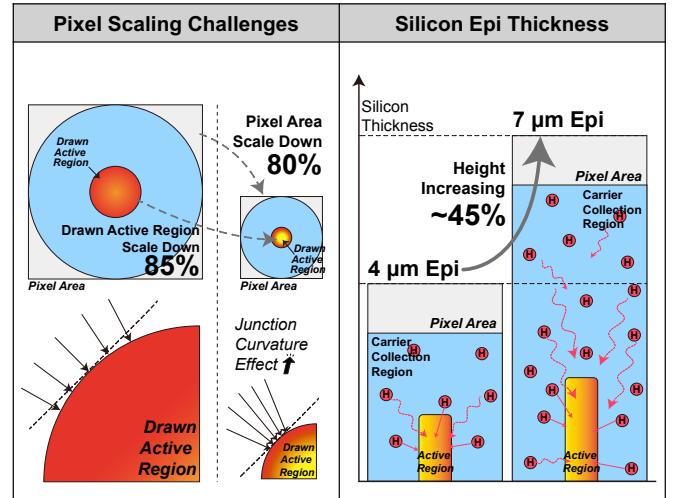

conjunction with this, the total silicon thickness is increased from 4 to 7  $\mu\text{m}$  to secure sufficient structural depth. The p-n junction diameter is also reduced from 2.5 to 1  $\mu\text{m}$  to accommodate the smaller pixel footprint. Both designs employ a p+/deep n-well (DNW) junction for avalanche multiplication, a p-well (PW) GR to suppress premature edge breakdown (PEB), and a BR to supply the operation voltage to the SPAD. To quantify the benefit of pixel miniaturization, Fig. 4 compares the required SPAD array area to implement a 1 Megapixel array using two different pixel pitches. The 8  $\mu\text{m}$  pitch requires 64  $\text{mm}^2$  of area, whereas the scaled 3.5  $\mu\text{m}$  design only occupies 12.25  $\text{mm}^2$ . This 5.2 $\times$  reduction in area directly translates to improved integration density and enables SPAD array implementation in compact form factors, such as mobile and wearable devices. These results highlight the critical importance of pixel scaling for realizing high-resolution SPAD imagers in practical applications. However, this miniaturization also introduces several drawbacks, as highlighted in Fig. 5. First, reducing the active area diameter from 2.5 to 1  $\mu\text{m}$  increases the curvature at the junction periphery, elevating the risk of PEB and degrading breakdown uniformity, which in turn reduces the PDP. Second, the

Fig. 5. Challenges in pixel scaling and mitigation via thicker epitaxial silicon.

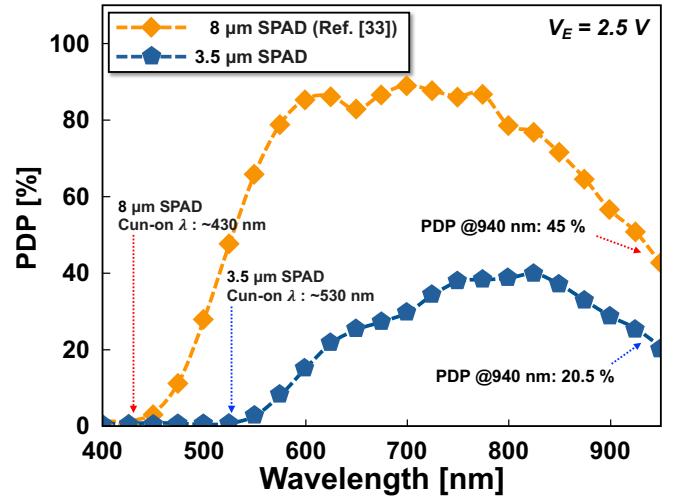

Fig. 6. Measured PDP spectra of 8  $\mu\text{m}$  pitch and proposed 3.5  $\mu\text{m}$  SPADs.

smaller active volume inherently limits the number of photogenerated carriers that can be efficiently collected, further diminishing sensitivity.

Fig. 6 presents the measured PDP of both SPADs at an excess bias voltage ( $V_E$ ) of 2.5 V. The scaled device exhibits lower PDP across the entire wavelength range. The cut-on wavelength shifts from 430 to 530 nm as the avalanche region is positioned deeper in the scaled device, causing short-wavelength carriers to recombine near the surface before multiplication. Most notably, the PDP at 940 nm drops from 45 to 20.5 %, clearly indicating a significant loss of NIR sensitivity. These findings demonstrate that while pixel miniaturization enhances integration density, it inevitably compromises photon detection performance. To address these challenges, precise control of the doping profiles and junction depth becomes essential. An optimized collection volume improves overall detection efficiency by facilitating more effective carrier collection. Therefore, further doping optimizations are required to recover high efficiency.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

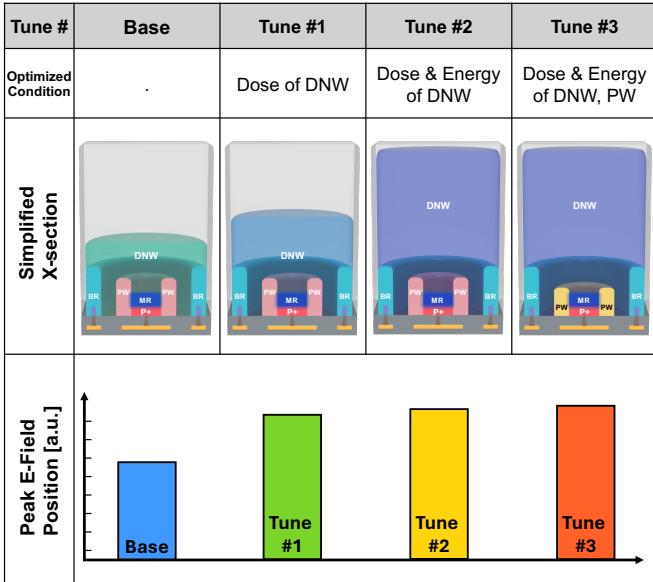

Fig. 7. Doping-optimization strategy with three tuning schemes and corresponding peak electric-field positions.

### III. DEVICE OPTIMIZATION PROGRESS

To overcome the degradation in PDP caused by aggressive pixel miniaturization, we implemented a systematic doping optimization strategy aimed at restoring collection efficiency and electric-field control. The approach involved adjusting the DNW and GR doping to enhance both carrier-collection and avalanche-triggering performance. We developed three tuning schemes—Tune #1, #2, and #3—each targeting a specific improvement, as summarized in Fig. 7. Tune #1 expands the DNW region by controlling the implanted dose, effectively increasing the n-type collection volume around the multiplication region (MR), which serves as the carrier-collection region. Tune #2 further enlarges the n-type volume by adjusting the dose and energy of DNW, extending the carrier-collection region vertically and laterally to improve detection efficiency. Tune #3 incorporates an optimized PW design in addition to Tune #2. This combined configuration not only maintains a large collection volume but also promotes a more efficient electric-field distribution, improving breakdown stability and overall SPAD performance. As shown in Fig. 7, the peak electric-field position gradually shifts upward with each tuning step, reflecting the deeper and more controlled field shaping. This evolution illustrates the critical role of DNW and GR engineering in recovering SPAD performance lost during pixel scaling.

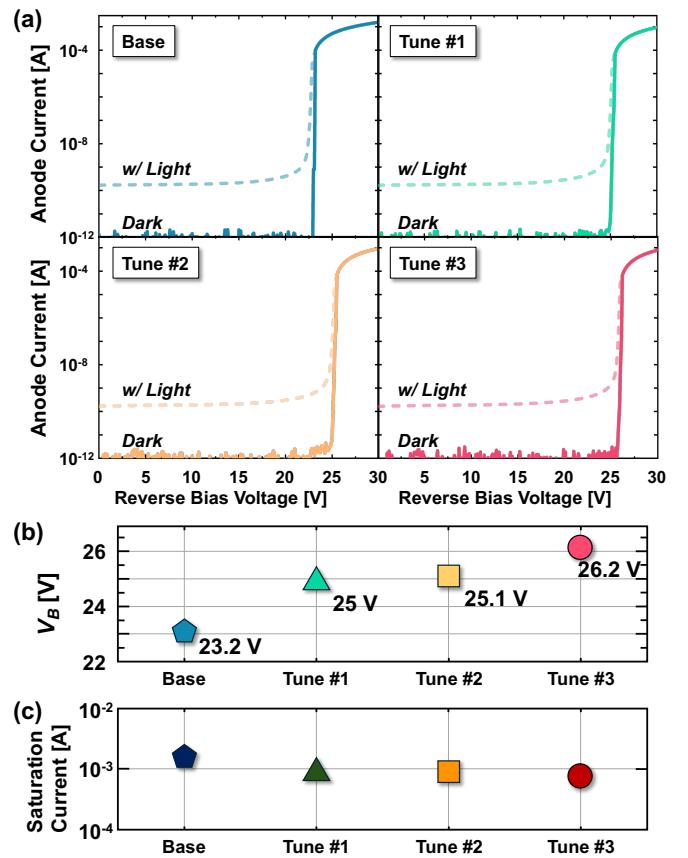

To validate the effectiveness of our structural tuning, we measured the electrical and optical characteristics of all four SPAD variants. As shown in Fig. 8(a), the current–voltage (I–V) characteristics under both dark and illuminated conditions demonstrate stable avalanche behavior across all configurations. Fig. 8(b) summarizes the breakdown voltage ( $V_B$ ) for each design. The  $V_B$  increases progressively from 23.2 V in the base structure to 26.2 V in Tune #3, which is attributed to the gradual extension of the depletion region and reshaping of the electric field caused by the DNW and GR

Fig. 8. Impact of doping optimization on SPAD electrical characteristics: (a) I–V curves under dark and illuminated conditions for each tuning step. (b)  $V_B$  and (c) saturation-current comparisons.

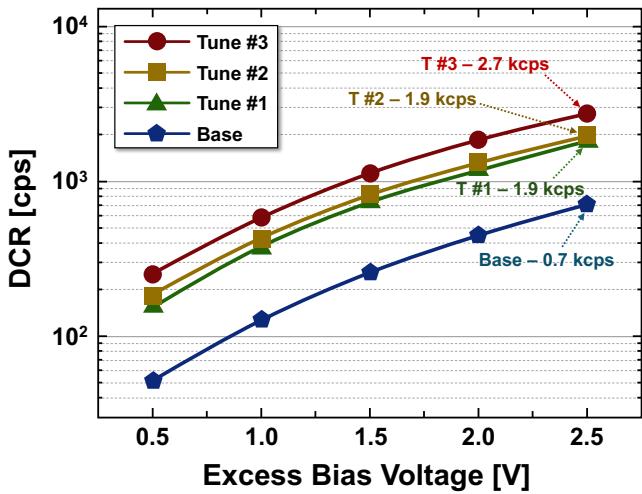

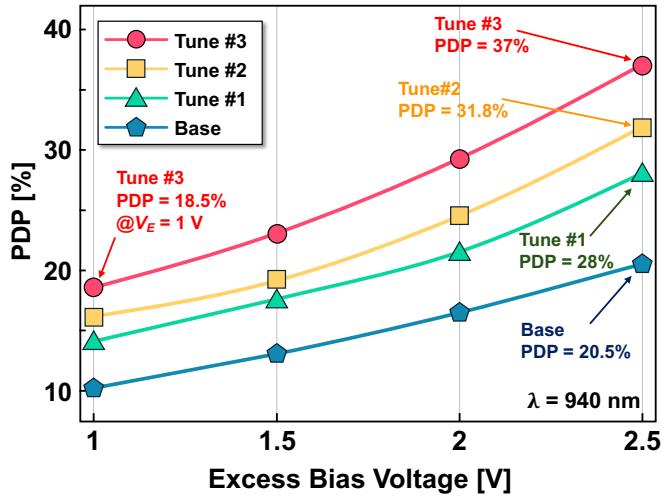

optimizations. The observed reduction in saturation current reflects the increased series resistance from anode to cathode, mainly resulting from the deeper and wider DNW. Fig. 9 presents the dark count rate (DCR) measured at room temperature across  $V_E$  ranging from 0.5 to 2.5 V in 0.5 V steps. The comparison includes the base structure and three tuning variants (Tune #1–#3). The base device exhibits the lowest DCR of approximately 0.7 kcps at  $V_E = 2.5$  V, whereas Tune #1 and Tune #2 show a moderate increase to around 1.9 kcps. Tune #3 exhibits the DCR of 2.7 kcps. The gradual increase in DCR across the tuning steps is attributed not to an increase in defect density but rather to the deliberate expansion of the carrier collection region and the enhancement of electric-field uniformity at the MR through DNW and GR engineering. Thus, the increase in DCR is a trade-off that accompanies the improved detection capability rather than a degradation of device quality. It is also important to note that for most outdoor applications, the DCR contribution becomes negligible compared to the dominant effect of ambient light. Therefore, the observed DCR values remain sufficiently low and acceptable for practical SPAD implementations. Fig. 10 presents the PDP characteristics of the Base and Tune #1–#3 structures measured at 940 nm. The  $V_E$  was swept from 1 to 2.5 V in 0.5 V increments. As doping and field-shaping optimizations progress from Base to Tune #3, PDP values improve consistently across all bias points. Notably, at  $V_E =$

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 9. DCR comparison across doping tuning conditions as a function of  $V_E$ .

Fig. 10. Measured PDP at 940 nm under various  $V_E$  for each doping-tuning condition.

Fig. 11. Measured PDP at 940 nm under various  $V_E$  for each doping-tuning condition.

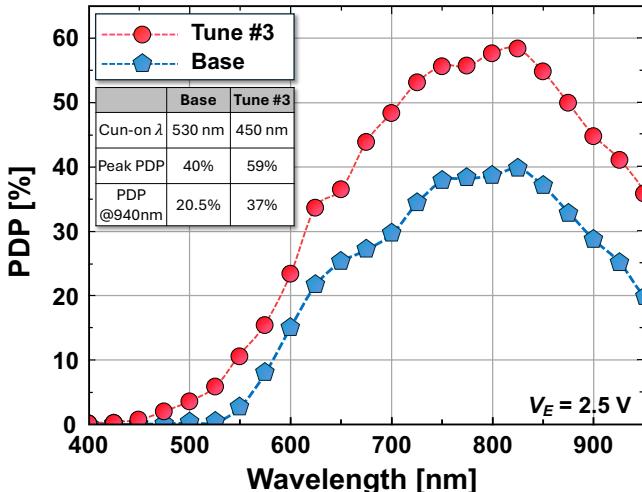

2.5 V, the PDP improved from 20.5% (Base) to 28% (Tune #1), 31.8% (Tune #2), and ultimately 37% (Tune #3). Even at  $V_E = 1$  V, the Tune #3 device achieved a PDP of 18.5%, which is comparable to that of the Base device at 2 V, indicating superior carrier collection and triggering efficiency under lower electric fields. These results validate that the electric-field optimization not only enhances triggering probability but also enables lower-voltage operation while maintaining high sensitivity. Fig. 11 shows the wavelength-dependent PDP response of the Base and Tune #3 SPADs at  $V_E = 2.5$  V and room temperature. Across the visible to near-infrared spectrum (400–950 nm), the Tune #3 device exhibits both higher peak performance and a broader spectral response. The peak PDP improved from 40% to 59% at 825 nm. At 940 nm, which is a key wavelength for many practical applications, PDP increased from 20.5% (Base) to 37% (Tune #3). Additionally, the cut-on wavelength—defined as the onset of significant PDP rise—shifted from 530 nm (Base) to 450 nm (Tune #3), suggesting improved blue-side response due to reduced absorption losses around the back-side surface. These enhancements are attributed to the optimized electric-field profile and doping gradient, which improve carrier-collection efficiency across a wider absorption depth range and avalanche-triggering probability.

The results in this section demonstrate that careful engineering of doping profiles—particularly expansion of the DNW and optimization of the GR—can effectively restore photon-detection performance degraded by pixel scaling. The final configuration (Tune #3) successfully recovers PDP to 37% at 940 nm, nearly doubling the efficiency of the base device. These findings highlight the viability of scaling SPAD pixels down to 3.5  $\mu$ m without significant compromise in sensitivity, provided that the device architecture is co-optimized with doping and design strategies.

#### IV. FULL CHARACTERIZATION OF THE OPTIMIZED SPAD

To assess the practical applicability of the proposed SPAD, we conducted comprehensive electrical and optical characterizations using the optimized structure, referred to as Tune #3. Key metrics such as temperature-dependent  $V_B$  and DCR, light-emission test (LET), timing jitter, and afterpulsing probability were measured.

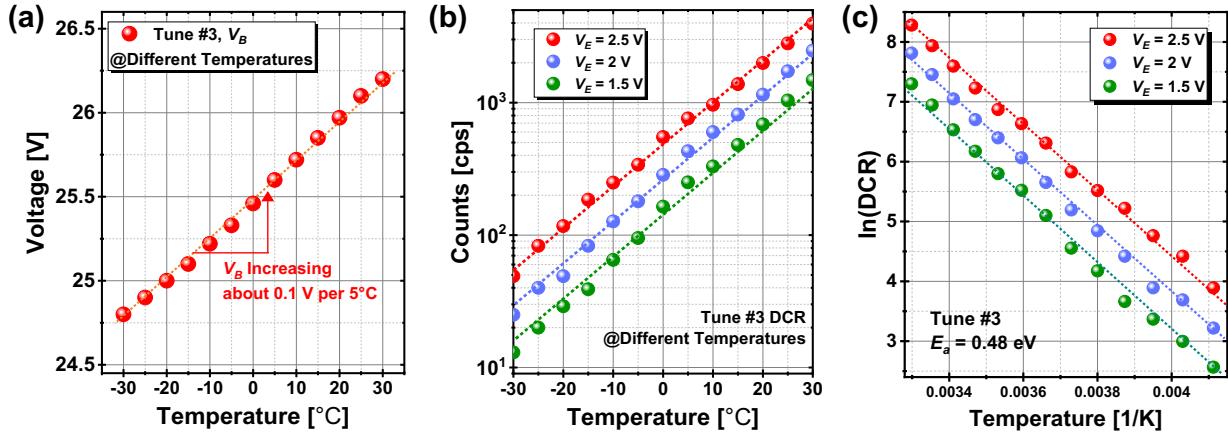

We investigated the thermal robustness of the optimized SPAD by measuring the  $V_B$  over a temperature range from  $-30$  to  $30$  °C in 5 °C increments. As shown in Fig. 12(a), the  $V_B$  exhibits a consistent and linear increase of approximately 0.1 V per 5 °C. Such linearity ensures predictable biasing behavior across a wide operating temperature window, which is particularly important for applications requiring stable gain and timing performance in outdoor or thermally dynamic environments. These results confirm that the optimized SPAD maintains excellent thermal stability, with no abrupt shifts or anomalies in  $V_B$ , thereby simplifying system-level bias control strategies. To evaluate thermal robustness and understand the temperature-induced behavior of the optimized SPAD, DCR was also measured from  $-30$  to  $+30$  °C in steps of 5 °C using a temperature-controlled environment chamber, and the results

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

are depicted in Fig. 12(b). DCR increases exponentially with temperature, consistent with thermally-generated carriers becoming more dominant at higher temperatures. To analyze this further, Arrhenius plots of DCR are presented in Fig. 12(c) for three  $V_E$  conditions. The extracted slopes correspond to an activation energy ( $E_a$ ) of approximately 0.48 eV, indicating that Shockley–Read–Hall (SRH) generation dominates the thermal contribution to DCR in this structure.

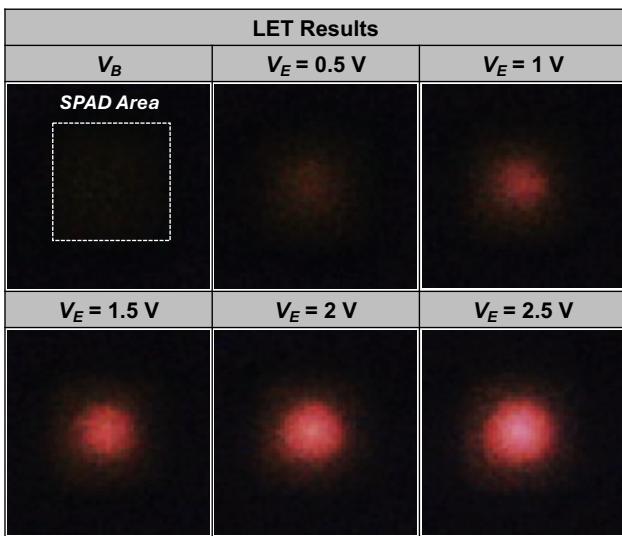

To visualize the avalanche multiplication region of the optimized SPAD, LET measurements were performed by increasing the  $V_E$  from 0.5 to 2.5 V. As  $V_E$  increases, light emission appears and strengthens, remaining well-centered within the SPAD active area. The results indicate a well-confined avalanche multiplication region and confirm that the optimized GR design effectively suppresses PEB.

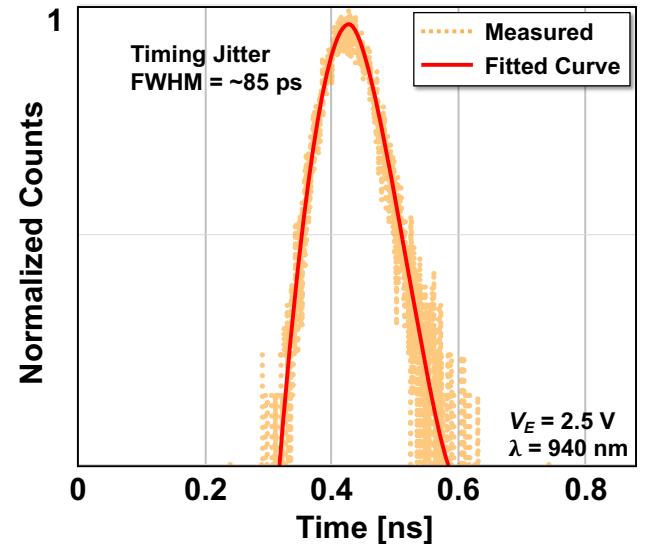

To evaluate the temporal resolution of the optimized SPAD, timing jitter was measured at  $V_E = 2.5$  V using a ps pulsed laser diode with a wavelength of 940 nm. The measurement setup captured the time distribution of the first

photon-triggered avalanche events. As shown in Fig. 14, the resulting timing jitter exhibits a full width at half maximum (FWHM) of approximately 85 ps. This result highlights the device's fast temporal response and suitability for time-resolved applications such as LiDAR and FLIM.

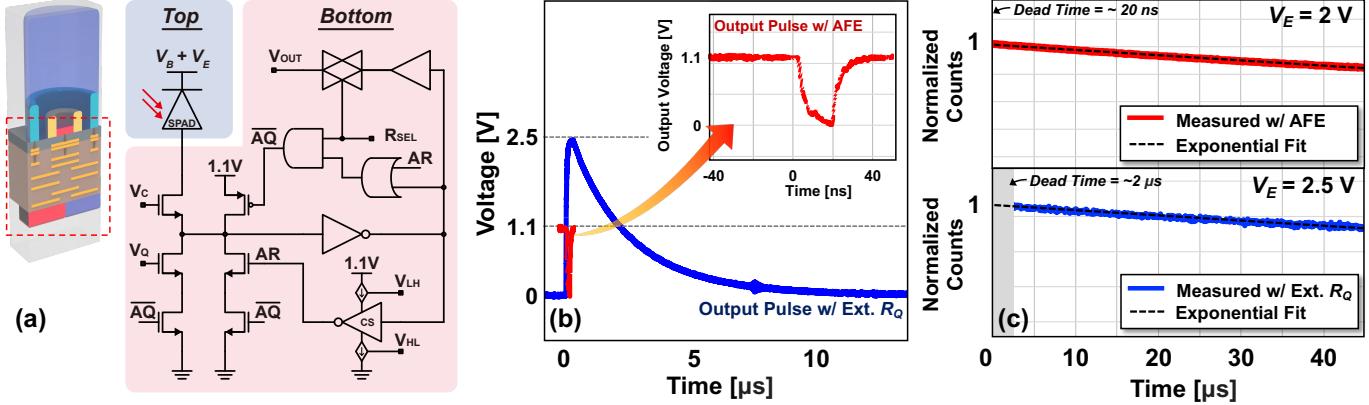

To evaluate the afterpulsing probability (APP) with minimal distortion, it is essential to reduce the dead time following an avalanche event. We employ an analogue front-end (AFE) circuit shown in the bottom-tier schematic (Fig. 15(a)) to minimize dead time and allow accurate time-domain analysis. All transistors are 1.1 V low-voltage (LV) devices, and a  $V_c$ -controlled cascode transistor is implemented to expand the circuit's accommodatable  $V_E$  range, which is approximately doubled. To suppress the afterpulse effect, an active quenching technique employing a positive feedback loop is implemented, which rapidly senses the avalanche current to turn off the quenching load transistor, thereby significantly increasing the load resistance. Concurrently, it enhances the active quenching effect by quickly injecting charges into the SPAD anode. This approach

Fig. 12. Temperature dependence of the optimized SPAD: (a)  $V_B$ , (b) DCR, and (c) Arrhenius analysis under different  $V_E$ .

Fig. 13. LET measurement results of the optimized SPAD under various  $V_E$ .

Fig. 14. Timing jitter histogram of the optimized SPAD measured at 940 nm under  $V_E = 2.5$  V.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 15. (a) SPAD (top-tier) and AFE (bottom-tier) schematic. (b) Output pulses and (c) inter-avalanche histograms with the AFE and external quenching resistor.

is also effective in mitigating the degradation of quenching speed caused by RC delay, which arises from the increased parasitic capacitance between the SPAD's output node and the front-end circuit's input in 3D-stacked Cu-to-Cu bonding. This front-end circuit also incorporates an active recharge function using a negative feedback loop to minimize the dead time for precise APP measurements. This feature facilitates a rapid reset by quickly removing residual charge in the SPAD after an adjustable delay. As illustrated in Fig. 15(b), the output pulse generated with an external quenching resistor ( $R_Q$ ) exhibits a relatively long tail (~2 μs dead time), primarily due to parasitic capacitance and setup-related factors. In contrast, using the integrated AFE enables a significantly shorter dead time down to ~20 ns, ensuring more precise measurement of the afterpulse distribution. Fig. 15(c) compares the afterpulsing histograms under both quenching configurations, and by integrating the front-end circuit, we could characterize the APP at much shorter dead times, which is difficult to achieve with discrete device measurements. The results confirm that the afterpulse effect is negligible even at the short dead time, demonstrating that the device is successfully optimized, implying a low concentration of trapping defects.

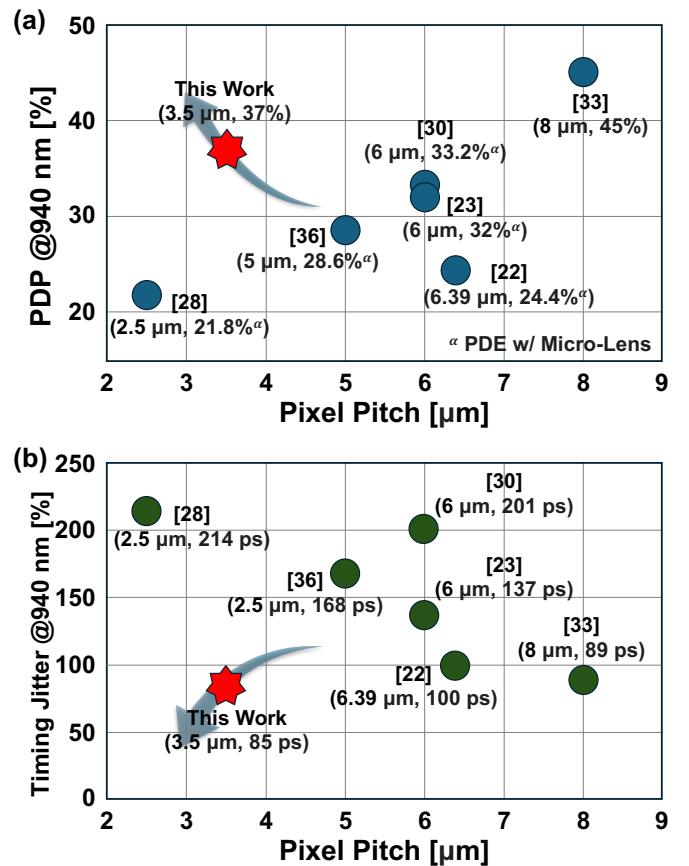

## V. COMPARISONS AND CONCLUSION

To evaluate the performance of the optimized SPAD, we benchmark key metrics—pixel pitch, dark count rate (DCR), photon detection probability (PDP), and timing jitter—against prior state-of-the-art SPADs fabricated in 3D-BI structures. As shown in Fig. 16(a), our device achieves a PDP of 37 % at 940 nm, which outperforms all previous works in the sub-5 μm pixel pitch regime. Notably, while Ref. [33]—prior 8 μm SPAD—reports the highest PDP of 45 %, it is achieved with a significantly larger pixel size. In this work, we aggressively reduce the pixel pitch by more than half to 3.5 μm, and yet successfully recover a substantial portion of the degraded PDP through doping profile optimization, achieving performance that exceeds many 6 μm and 5 μm devices. In Fig. 16(b), the timing jitter of our SPAD is measured as 85 ps at 940 nm, which represents the lowest value among all surveyed 3D-BI SPADs regardless of pitch. Even compared to 8 μm devices

Fig. 16. Comparison with state-of-the-art 3D-stacked BI SPADs at 940 nm: (a) PDP and (b) timing jitter versus pixel pitch.

with 89 ps jitter [33], the proposed SPAD demonstrates enhanced timing resolution with 3.5 μm pixel integration, enabled by minimized carrier transit paths and optimized avalanche triggering. As summarized in Table I, our SPAD is fabricated using an advanced 40 nm node, and through careful optimization, we achieve one of the smallest pixel pitches to date among 3D-BI SPADs, while preserving excellent performance.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

In this work, we demonstrate a 3.5  $\mu\text{m}$ -pitch 3D-stacked BI SPAD fabricated in a 40 nm CIS process, achieving a PDP of 37% and a timing jitter of 85 ps at 940 nm. This performance represents a significant advancement over prior SPADs with similar or larger pitches, particularly considering the aggressive scaling from our previous 8  $\mu\text{m}$ -pitch device. While pixel miniaturization typically compromises device efficiency and timing precision, our miniaturized SPAD successfully recovers performance through vertical-layer engineering and doping-profile optimization. In particular, we highlight that this work demonstrates one of the smallest pixel pitches among reported 3D-BI SPADs without sacrificing device performance. The combination of high PDP, low jitter, and small pitch makes this SPAD a promising candidate for compact depth-sensing systems such as LiDAR and 3D imaging in mobile and wearable applications.

TABLE I

PERFORMANCE COMPARISON OF STATE-OF-THE-ART

3D-STACKED BI SPADS

| Parameter                     | This Work            | [22]<br>IEDM'21   | [23]<br>IEDM'21   | [28]<br>IEDM'22   | [30]<br>VLSI'23   | [33]<br>JSTQE'24 | [36]<br>IEDM'24   |

|-------------------------------|----------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|

| Technology [nm]               | <b>40</b><br>(3D-BI) | 90<br>(3D-BI)     | 90<br>(3D-BI)     | 90<br>(3D-BI)     | 90<br>(3D-BI)     | 40<br>(3D-BI)    | 90<br>(3D-BI)     |

| Pixel Pitch [ $\mu\text{m}$ ] | <b>3.5</b>           | 6.39              | 6                 | 2.5               | 6                 | 8                | 5                 |

| $V_g$ [V]                     | <b>26.2</b>          | 30                | 22                | 18                | 22                | 23.3             | 21.2              |

| $V_E$ [V]                     | <b>2.5</b>           | 2.5               | 3                 | 3                 | 3                 | 2.5              | 3                 |

| DCR [cps/pix]                 | <b>2722</b>          | 1.8               | 19                | 173               | 221 <sup>a</sup>  | 27 <sup>b</sup>  | 5                 |

| PDP @905 nm [%]               | <b>44.7</b>          | 28 <sup>y</sup>   | 32 <sup>y</sup>   | -                 | 43 <sup>y</sup>   | 58               | 36 <sup>y</sup>   |

| PDP @940 nm [%]               | <b>37</b>            | 24.4 <sup>y</sup> | 20.2 <sup>y</sup> | 21.8 <sup>y</sup> | 33.2 <sup>y</sup> | 45               | 28.6 <sup>y</sup> |

| Timing Jitter @ 940 nm [ps]   | <b>85</b>            | 100               | 137               | 214               | 201               | 89               | 168               |

<sup>a</sup>Measured @60°C, <sup>b</sup>cps/ $\mu\text{m}^2$ , <sup>y</sup>PDE w/ Micro-Lens

## REFERENCES

- [1] M. Kim, H. Seo, S. Kim, J.-H. Chun, S.-J. Kim, and J. Choi, "A 320x240 CMOS LiDAR sensor with 6-transistor nMOS-only SPAD analog front-end and area-efficiency priority histogram memory," *Int. Solid-State Circ. Conf.*, 2025.

- [2] C. Bruschini, H. Homulle, I. M. Antolovic, S. Burri, and E. Charbon, "Single-photon avalanche diode imagers in biophotonics: review and outlook," *Light: Sci. Appl.*, vol. 8, no. 1, Sep. 2019.

- [3] H.-S. Choi, I. Park, B. Park, D. Cho, M.-J. Lee, and Y. Chae, "SPAD flash LiDAR with chopper analog counter for 76 m range and 120 klx background light," *Int. Solid-State Circ. Conf.*, 2025.

- [4] R. H. Hadfield, "Single-photon detectors for optical quantum information applications," *Nature Photonics*, vol. 3, no. 12, pp. 696-705, 2009.

- [5] X. Qian, W. Jiang, and M. J. Deen, "Single photon detectors for automotive LiDAR applications: state-of-the-art and research challenges," *IEEE J. Sel. Topics Quantum Electron.*, vol. 30, no. 1, Jan./Feb. 2024.

- [6] Z. Ebrahimi, and B. Gosselin, "Photodetector innovations for advancing wearable optical biosensors: a review," *IEEE Sensors J.*, vol. 25, no. 3, Feb. 2025.

- [7] E. Park, W.-Y. Choi, and M.-J. Lee, "Optical and electrical characterization of single-photon avalanche diodes fabricated in CMOS technology," *IEEE Int. Conf. Consum. Electron.-Asia*, 2024.

- [8] E. Park, W.-Y. Ha, H.-S. Park, D. Eom, H.-S. Choi, D.-H. Ahn, W.-Y. Choi, and M.-J. Lee, "A back-illuminated SPAD fabricated with 40 nm CMOS image sensor technology achieving near 40% PDP at 940 nm," *IEEE J. Sel. Topics Quantum Electron.*, vol. 30, no. 1, Jan./Feb. 2024.

- [9] S. Burri, Y. Maruyama, X. Michalet, F. Regazzoni, C. Bruschini, and E. Charbon, "Architecture and applications of a high resolution gated SPAD image sensor," *Opt. Express*, vol. 22, no. 14, 2024.

- [10] N. A. W. Dutton, L. Parmesan, L. J. Holmes, L. A. Grant, and R. K. Henderson, "320x240 oversampled digital single photon counting image sensor," *Symp. VLSI Circ. Tech.*, 2024.

- [11] N. Krstajić, R. Walker, J. Levitt, S. P. Poland, D. Li, S. Ameer-Beg, and R. K. Henderson, "A 256 x 8 SPAD line sensor for time resolved fluorescence and raman sensing," *European Solid-State Circ. Conf.*, 2014.

- [12] N. Krstajić, J. Levitt, S. Poland, S. Ameer-Beg, and R. K. Henderson, "256 x 2 SPAD line for time resolved fluorescence spectroscopy," *Opt. Express*, vol. 23, no. 5, 2015.

- [13] L. Parmesan, N. A. W. Dutton, N. J. Calder, N. Krstajić, A. J. Holmes, L. A. Grant, and R. K. Henderson, "A 245 x 256 SPAD array with in-pixel time to amplitude conversion for fluorescence lifetime imaging microscopy," *Int. Image Sensor Workshop*, 2015.

- [14] J. M. Pavia, M. Scandini, S. Lindner, M. Wolf, and E. Charbon, "A 1 x 400 backside-illuminated SPAD sensor with 49.7 ps resolution, 30 pJ/sample TDCs fabricated in 3D CMOS technology for near-infrared optical tomography," *IEEE J. Solid-State Circ.*, vol. 50, no. 10, Oct. 2015.

- [15] T. Al. Abbas, N. A. W. Dutton, O. Almer, S. Pellegrini, Y. Henrion, and R. K. Henderson, "Backside illuminated SPAD image sensor with 7.83  $\mu\text{m}$  pitch in 3D-stacked CMOS technology," *Int. Electron Devices Meeting*, 2016.

- [16] M. Perenzoni, N. Massari, D. Perenzoni, L. Gasparini, and D. Stoppa, "Imager with time-gating and self-referenced column-parallel A/D conversion for fluorescence lifetime imaging," *IEEE J. Solid-State Circ.*, vol. 51, no. 1, 2016.

- [17] A. C. Ulku, C. Bruschini, X. Michalet, S. Weiss, and E. Charbon, "A 512 x 512 SPAD image sensor with built-in gating for phasor based real-time siFLIM," *Int. Image Sensor Workshop*, 2017.

- [18] I. Gyongy, N. Calder, A. Davies, N. A. W. Dutton, R. R. Duncan, C. Rickman, P. Dalgarno, and R. K. Henderson, "A 256 x 256, 100-kfps, 61% fill-factor SPAD image sensor for time-resolved microscopy applications," *IEEE Trans. Electron Devices*, vol. 65, no. 2, Feb. 2018.

- [19] A. R. Ximenes, P. Padmanabhan, M.-J. Lee, Y. Yamashita, D. N. Yaung, and E. Charbon, "A 256x256 45/65nm 3D-stacked SPAD-based direct TOF image sensor for LiDAR applications with optical polar modulation for up to 18.6dB interference suppression," *Int. Solid-State Circ. Conf.*, 2018.

- [20] R. K. Henderson, N. Johnston, S. W. Hutchings, I. Gyongy, T. Al. Abbas, N. Dutton, M. Tyler, S. Chan, and J. Leach, "A 256x256 40nm/90nm CMOS 3D-stacked 120dB-dynamic-range reconfigurable time-resolved SPAD imager," *Int. Solid-State Circ. Conf.*, 2019.

- [21] K. Ito, Y. Otake, Y. Kitano, A. Matsumoto, J. Yamamoto, T. Ogashara, H. Hiyama, R. Naito, K. Takeuchi, T. Tada, K. Takabayashi, H. Nakayama, K. Tatani, T. Hirano, and T. Wakano, "A back illuminated 10  $\mu\text{m}$  SPAD pixel array comprising full trench isolation and Cu-Cu bonding with over 14% PDE at 940 nm," *Int. Electron Devices Meeting*, 2020.

- [22] K. Morimoto, J. Iwata, M. Shinohara, H. Sekine, A. Abdelghafar, H. Tsuchiya, Y. Kuroda, K. Tojima, W. Endo, Y. Maehashi, Y. Ota, T. Sasago, S. Maekawa, S. Hikosaka, T. Kanou, A. Kato, T. Tezuka, S. Yoshizaki, T. Ogawa, K. Uehira, F. Inui, Y. Matsuno, K. Sakurai, and T. Ichikawa, "3.2 megapixel 3D-stacked charge focusing SPAD for low-light imaging and depth sensing," *Int. Electron Devices Meeting*, 2021.

- [23] S. Shimada, Y. Otake, S. Yoshida, S. Endo, R. Nakamura, H. Tsugawa, T. Ogita, T. Ogashara, K. Yokochi, Y. Inoue, K. Takabayashi, H. Maeda, K. Yamamoto, M. Ono, S. Matsumoto, H. Hiyama, and T. Wakano, "A back illuminated 6  $\mu\text{m}$  SPAD pixel array with high PDE and timing jitter performance," *Int. Electron Devices Meeting*, 2021.

- [24] J. Ogi, T. Takasuka, K. Hizu, Y. Inaoka, H. Zhu, Y. Tochigi, Y. Tashiro, F. Sano, Y. Murakawa, M. Nakamura, and Y. Oike, "A 124-dB dynamic-range SPAD photon-counting image sensor using subframe

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

sampling and extrapolation photon count," *IEEE J. Solid-State Circ.*, vol. 56, no. 11, Nov. 2021.

[25] O. Kumagai, J. Ohmachi, M. Matsumura, S. Yagi, K. Tayu, K. Amagawa, T. Matsukawa, O. Ozawa, D. Hiroto, Y. Shinozuka, R. Homma, K. Mahara, T. Ohyama, Y. Morita, S. Shimada, T. Ueno, A. Matsumoto, Y. Otake, T. Wakano, and T. Izawa, "A 189x600 back-illuminated stacked SPAD direct time-of-flight depth sensor for automotive LiDAR systems," *Int. Solid-State Circ. Conf.*, 2021.

[26] W. Sun, Y. Wang, M. Liu, and Y. Yang, "A back-illuminated 4 $\mu$ m P+N-well single photon avalanche diode pixel array with 0.36Hz/ $\mu$ m<sup>2</sup> dark count rate at 2.5 V excess bias voltage," *IEEE Electron. Device Lett.*, vol. 43, no. 9, 2022.

[27] Y. Ota, K. Morimoto, T. Sasago, M. Shinohara, Y. Kuroda, W. Endo, Y. Maehashi, S. Maekawa, H. Tsuchiya, A. Abdelghafar, S. Hikosaka, M. Motoyama, K. Tojima, K. Uehira, J. Iwata, F. Inui, Y. Matsuno, K. Sakurai, and T. Ichikawa, "A 0.37W 143dB-dynamic-range 1Mpixel backside-illuminated charge-focusing SPAD image sensor with pixel-wise exposure control and adaptive clocked recharging," *Int. Solid-State Circ. Conf.*, 2022.

[28] S. Shimada, Y. Otake, S. Yoshida, Y. Jibiki, M. Fujii, S. Endo, R. Nakamura, H. Tsugawa, Y. Fujisaki, K. Yokochi, J. Iwase, K. Takabayashi, H. Maeda, K. Sugihara, K. Yamamoto, M. Ono, K. Ishibashi, S. Matsumoto, H. Hiyama, and T. Wakano, "A SPAD depth sensor robust against ambient light: the importance of pixel scaling and demonstration of a 2.5 $\mu$ m pixel with 21.8% PDE at 940nm," *Int. Electron Devices Meeting*, 2022.

[29] J. Ogi, F. Sano, T. Nakata, Y. Kubo, W. Onishi, C. Koswaththage, T. Mochizuki, Y. Tashiro, K. Hizu, T. Takatsuka, I. Watanabe, F. Koga, T. Hirano, and Y. Oike, "A 3.06  $\mu$ m single-photon avalanche diode pixel with embedded metal contact and power grid on deep trench pixel isolation for high-resolution photon counting," *Sensors*, vol. 23, no. 21, 2023.

[30] Y. Fujisaki, H. Tsugawa, K. Sakai, H. Kumagai, R. Nakamura, T. Ogita, S. Endo, T. Iwase, H. Takase, K. Yokochi, S. Yoshida, S. Shimada, Y. Otake, T. Wakano, H. Hiyama, K. Hagiwara, M. Arakawa, S. Matsumoto, H. Maeda, K. Sugihara, K. Takabayashi, M. Ono, K. Ishibashi, and K. Yamamoto, "A back-illuminated 6  $\mu$ m SPAD depth sensor with PDE 36.5% at 940 nm via combination of dual diffraction structure and 2x2 on-chip lens," *Symp. VLSI Circ. Tech.*, 2023.

[31] E. Park, D. Eom, J.-H. Kim, H. An, S. Yi, K.-D. Kim, J. Kim, H.-S. Oh, W.-Y. Choi, and M.-J. Lee, "Back-illuminated SPAD in 40 nm CIS technology achieving 56 ps timing jitter with 15 V breakdown voltage for short/mid-range LiDAR applications," *Int. Electron Devices Meeting*, 2023.

[32] T. Takatsuka, J. Ogi, Y. Ikeda, K. Hizu, Y. Inaoka, S. Sakama, I. Watanabe, T. Ishikawa, S. Shimada, J. Suzuki, H. Maeda, K. Toshima, Y. Nonaka, A. Yamamura, H. Ozawa, F. Koga, and Y. Oike, "A 3.36- $\mu$ m-pitch SPAD photon-counting image sensor using a clustered multi-cycle clocked recharging technique with an intermediate most-significant-bit readout," *IEEE J. Solid-State Circ.*, vol. 59, no. 14, Apr. 2024.

[33] E. Park, D. Eom, M.-H. Yu, Y.-M. Moon, D.-H. Ahn, J. Ahn, D. K. Hwang, W.-Y. Choi, and M.-J. Lee, "Back-illuminated double-avalanche-region single-photon avalanche diode," *IEEE J. Sel. Topics Quantum Electron.*, vol. 30, no. 1, Jan./Feb. 2024.

[34] D. Moschella, D. Berretta, F. Villa, and A. Tosi, "A 64  $\times$  64 SPAD array for quantum ghost imaging with integrated TDCs and event-driven readout in a 40 nm CMOS Technology," *Conf. PhD Research Microelectron. and Electron.*, 2024.

[35] F. Mattioli Della Rocca, E. J. Sie, A. T. Erdogan, L. Fisher, A. B. Matheson, N. Finlayson, A. Gorman, I. Gyongy, H. Mai, T. Lachaud, R. Forsyth, F. Marsili, and R. K. Henderson, "A 512x512 SPAD laser speckle autocorrelation imager in stacked 65/40nm CMOS," *Symp. VLSI Circ. Tech.*, 2024.

[36] J. Ogi, S. Kitamura, F. Sugaya, J. Suzuki, A. Magori, T. Matsui, K. Sumita, Y. Ushiku, K. Moriyama, K. Toshima, T. Namise, H. Ozawa, Y. Tsukuda, Y. Otake, H. Hiyama, S. Matsumoto, A. Suzuki, and F. Koga, "A 2.1-ns dead time 5- $\mu$ m single photon avalanche diode with 2-layer transistor pixel technology," *Int. Electron Devices Meeting*, 2024.

[37] Y. Liu, R. Fan, Y. Zhao, J. Hu, R. Ma, and Z. Zhu, "A junction-optimized SPAD with 50.6% peak PDP and 0.64 cps/ $\mu$ m<sup>2</sup> DCR at 2 V excess bias voltage in 130 nm CMOS," *IEEE Electron. Device Lett.*, vol. 45, no. 3, 2024.

[38] K. Morimoto, N. Isoda, H. Sekine, T. Sasago, Y. Maehashi, S. Mikajiri, K. Tojima, M. Shinohara, A. Abdelghafar, H. Tsuchiya, K. Inoue, S. Omodani, K. Chida, A. Ehara, J. Iwata, T. Itano, Y. Matsuno, K. Sakurai, and T. Ichikawa, "3D-stacked 1Megapixel time-gated SPAD image sensor with 2D interactive gating network for image alignment-free sensor fusion," *Symp. VLSI Circ. Tech.*, 2024.

[39] E. Park, H.-S. Park, H.-S. Choi, J.-H. Kim, D. Eom, E.-J. Kim, S. Yook, D.-H. Son, H. Lee, J. Jang, K.-D. Kim, J. Kim, W.-Y. Choi, and M.-J. Lee, "Optimization of a 3.5  $\mu$ m Pitch 3D-stacked back-illuminated SPAD in 40 nm CIS technology: achieving 37% PDP at 940 nm," *Symp. VLSI Circ. Tech.*, 2025.

**Eunsung Park** received his B.S. degree in Electronic Engineering from Gachon University, Gyeonggi-do, South Korea, in 2019. He is currently pursuing integrated M.S. and Ph.D. degrees in Electrical and Electronic Engineering at Yonsei University. From 2019 to 2024, he was a Student Researcher at the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea. His research focuses on single-photon detection technologies, including silicon single-photon avalanche diodes (Si-SPADs), silicon photomultipliers (SiPMs), CMOS-based SPAD integration, and advanced CMOS image sensor (CIS) technologies.

sensors.

**Hyo-Sung Park** received the B.S. degree in semiconductor science & technology from Jeonbuk National University, Jeonju, South Korea, in 2020. He is currently working toward the M.S. and Ph.D. degrees with Yonsei University, Seoul, South Korea. From 2020 to 2024, he was a Student Researcher at the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea. His research interests include CMOS SPAD pixel and array circuits for photon-counting image sensors and LiDAR/D-ToF

**Hyun-Seung Choi** received the B.S. degree in electrical and electronic engineering from Chung-Ang University, Seoul, South Korea, in 2021. Since 2021, he has been working toward the M.S. and Ph.D. degrees with the Korea Institute of Science and Technology, Yonsei University, Seoul, South Korea. His research interests include single-photon avalanche diodes, LiDAR sensors and applications, and equivalent circuit modeling for CMOS SPADs.

> REPLACE THIS LINE WITH YOUR MANUSCRIPT ID NUMBER (DOUBLE-CLICK HERE TO EDIT) <

**Woo-Young Choi** (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1986, 1988, and 1994, respectively. His doctoral dissertation concerned the investigation of molecular-beam grown InGaAlAs laser diodes for fiber-optic applications. From 1994 to 1995, he was a Postdoctoral Research Fellow at NTT Opto-Electronics Laboratories, where he worked on femtosecond all-optical switching devices based on low-temperature grown InGaAlAs quantum wells. In 1995, he joined the Department of Electrical and Electronic Engineering, Yonsei University, Seoul, South Korea, where he is currently a Professor. His research interests include high-speed electronic circuits, silicon photonics, and Si image sensors.

**Myung-Jae Lee** (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Postdoctoral Researcher with the faculty of electrical engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applications based on single-photon avalanche diodes. In 2017, he joined the school of engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. From 2019 to 2024, he was a Principal Investigator / Principal Research Scientist with Korea Institute of Science and Technology (KIST), South Korea, where he led the research and development of SPAD and SiPM detectors/sensors for LiDAR, biomedical, and quantum applications. Since 2024, he has been an Associate Professor with Yonsei University, South Korea, where he has led the research and development of silicon photonics and optical interconnects as well as next-generation SPAD/SiPM/APD detectors/sensors for various applications. His research interests have spanned from photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof (e.g., LiDAR, ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, optical interconnects, etc.).