# 2009 Sonference

# 2009년도 **SoC** 학술대회

http://soc2009.chonbuk.ac.kr

일 시: **2009**년 **5**월 **15**일 (금) 19:00 - 21:30 (리셉션) **5**월 **16**일 (토) 09:00 - 17:00 (학술제)

장 소: 전주 한옥마을 (리셉션) 전북대학교 진수당 (학술제)

주 최: 대한전자공학회 SoC 설계 연구회

주 관: 전북대학교 BK21 전자정보고급인력양성사업단 ETRI 시스템반도체진흥센터

후 원: IDEC, KETI, 마그마 코리아, 한국멘토, 휴인스, 한백전자, Synopsys, 리버트론, IEEE CAS Seoul Chapter,

IEEE SSCS Seoul Chapter

#### 2009년도 S●C 학술대회

Session G1 : 09:00 ~ 10:30 Room 바오로홀

Core-A

좌장 : 이기준 (충남대)

G1.1 고성능 Core-A 임베디드 프로세서 구조

이광엽(서경대)

G1.2 GCC 포팅을 통한 Core-A C 컴파일러 개발

양원용, 이종열(전북대)

G1.3 Core-A Debugger 및 ICE

박형배. 지정훈, 허경철, 우균, 박주성(부산대)

G1.4 Core-A와 인터페이스 가능한 암호 모듈의 설계 성광주, 하창수, 엄창환, 임재환, 최병윤(동의대)

Session A2 : 13:30 ~ 15:00 Room 201

Oscillators

좌장: 이종욱 (경희대)

A2.1 자동 진폭 조절기능을 가진 350uW 3.2GHz 전압제어 발진기의 설계 김상우, 박준성, 부영건, 이강윤(건국대) 나유삼(삼성전기)

A2.2 저전력 CMOS 차동 지연 셀을 이용한 VCO 및 Prescaler 설계 박성식, 이주상, 유상대(경북대학교)

#### A2.3 피드포워드 방식 링 오실레이터에 대한 분석 및 스피드 최적화

박영석, 최우영(연세대) 한평수(LG전자)

A2.4 부 스큐 지연 방식 링 발진기의 해석\*

이정광. 정항근(전북대)

A2.5 A Wide Tuning Low Phase Noise PMOS Tuned-in Tuned-Out Voltage Controlled Oscillator

Tai Nghia Nguyen, 황상현, 이종욱(경희대)

A2.6 Dual Band(2.4/5.2GHz) CMOS VCO using Balanced Frequency Doubler with Gate Bias Matching Network

최성선, 유한열, 김용훈(광주과학기술원)

# 피드포워드 방식 링 오실레이터에 대한 분석 및 스피드 최적화

박영석<sup>1</sup>, 한평수<sup>2</sup>, 최우영<sup>1</sup>

<sup>1</sup>연세대학교 전기전자공학과 <sup>2</sup>LG electronics

전화: (02)2123-7709, E-mail: circuit@tera.yonsei.ac.kr

# Analysis and Speed Optimization of Feed Forward Ring Oscillators

Young-Seok Park<sup>1</sup>, Pyung-Su Han<sup>2</sup>,Woo-Young Choi<sup>1</sup>

Department of Electrical and Electronic Engineering. Yonsei University, <sup>2</sup>LG electronics

#### 요 익

본 논문에서는, 피드포워드 방식 링 오실레이터의 지연 스테이지를 소신호 분석과 중첩이론을 이용해서 쉽게 분석이 가능한 하나의 인풋을 가지는 지연 스테이지로 모델링을 하였다. 피드포워드 방식의 링 오실레이터는 여러 가지 다른 조건으로 발진하는 것이 가능하다는 것을 확인하였고, 오실레이터가 가장 빠른 발진 주파수를 가질 수 있는 조건을 예측하였다. 설계된 오실레이터의 포스트레이아웃 시뮬레이션 결과 0.18- $\mu$ m 공정을 사용하여 12 $\mu$ m 발진주파수를 가진다.

#### Abstract

In this paper, the feed forward ring oscillator unit stage is modeled as a single input amplifier using small signal analysis and superposition principle. Multiple oscillation mode are derived, and the dominant mode is predicted. Post layout simulation results show that 12-GHz oscillation frequency is achievable with a typical  $0.18-\mu\text{m}$  CMOS technology

Keywords: feed forward ring oscillator, oscillation frequency optimization, delay cell modeling

## I. 서 론

링 타입의 오실레이터는 파워 효율이 좋고, 넓은 주파수 조절 범위를 가지며, 무엇보다도 굉장히 작은 다이 면적을 차지하는 장점이 있어 클락 생성회로로서 널리 사용되고 있다. 게다가 링 오실레이터는 다중 위상을 가지는 클락 신호를 만들 수 있어 디지털 DLL 이나, CDR 과 같은 응용분야에 유용하게 쓰인다.

링 오실레이터의 발진 주파수는 보통 다음과 같이 계 산이 가능하다.

$$f_{OSC} = 1/(2Nt_d) \tag{1}$$

여기서 N 은 지연 스테이지의 개수를 나타내며,  $t_d$ 는 하나의 지연 스테이지가 가지는 지연 시간을 의미한다. 링 오실레이터의 발진 주파수는 N 에 반비례하기때문에 많은 지연 스테이지를 썼을 때 얻을 수 있는 동작 신뢰도의 향상과 많은 다중 위상 클락 신호라는 장점들이 반감된다.

이 한계를 극복하기 위해서 몇 가지 타입의 링 오실 레이터들이 개발되었는데<sup>[1~2]</sup>, 이들은 모두 기존 방식 의 오실레이터에 피드포워드 경로를 추가한 구조이다. 그중에는 LC 오실레이터와 비견될 정도로 높은 발진 주파수를 보이는 오실레이터도 있다<sup>[3]</sup>.

하지만, 현재까지는 피드포워드 방식의 링 오실레이 터에 대한 정확한 분석이 되고 있지 않아서 설계자들은 많은 시행착오를 거쳐서 디자인을 하고 있다. 본 논문에서는 피드포워드 방식의 링 오실레이터에 대한 새로운 모델과 함께, 발진 주파수를 최적화 할 수 있는 디자인 방법을 제시하였다.

# Ⅱ. 본 론

- 1. 피드포워드 링 오실레이터에 대한 분석

- 가. 주파수 응답

- 링 오실레이터의 발진 조건은 다음과 같다.

- 1) 각 스테이지에서의 위상 변화의 합이  $2\pi$ 의 정수배가 되어야 한다.

- 2) 링 오실레이터 루프의 전압이득이 1보다 커야한다.

그림 1. 5개의 지연 스테이지를 가지는 피드포워드 링 오 실레이터의 개념도

Fig. 1. Schematic diagram of a five-stage feed forward ring oscillator

그림 1은 5개의 지연 스테이지를 가지는 피드포워드 링 오실레이터에 대한 개념도이다. 이는 5개의 똑같은 지연 스테이지를 가지는 데, 지연 스테이지는 회색으로 표현되어 있다. 그림 1에서  $\alpha$  는 기본루프를 이루고 있는 직접 경로의 인버터와 피드포워드 경로의 인버터의 크기 비율로서 결국은 피드포워드 경로의 비중을 의미한다.

그림 2. 5개의 클락 신호들 간의 위상 관계

- (a) mode1  $(\theta_1=2\pi/5)$  (b) mode2  $(\theta_2=4\pi/5)$

- (c) mode3 ( $\theta_3=6\pi/5$ ) (d) mode4 ( $\theta_4=8\pi/5$ )

Fig. 2. Phase relationships of 5 clock signals

- (a) mode1 ( $\theta_1=2\pi/5$ ) (b) mode2 ( $\theta_2=4\pi/5$ )

- (c) mode3 ( $\theta_3=6\pi/5$ ) (d) mode4 ( $\theta_4=8\pi/5$ )

5개의 지연 스테이지를 가지는 링 오실레이터는 5개의 서로 다른 위상을 가지는 CKO~CK4까지의 클락 신

호를 생성한다. 이 5개의 클락 신호들은 서로 일정한 위상 관계를 가지고 있으며, 가장 인접한 두 클락 신호 가 가질 수 있는 모든 위상 관계는 그림 2와 같다. 각각의 위상 관계를 각각 mode 1,2,3,4로 이름붙이겠다.

기존 방식의 링 오실레이터의 경우 지연 스테이지가 가지는 위상 변화가  $\pi$  에서부터  $\pi/2$  까지 이기 때문에  $mode2(\theta_2=4\pi/5)$  의 위상 관계만이 발진 조건을 만족시킬 수 있다.

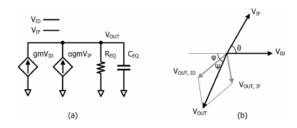

그림 3(a)은 피드포워드 방식의 링 오실레이터의 지연 스테이지에 대한 소신호 등가회로를 나타낸 것이다. 지연 스테이지는 편의를 위해 인버터로 결정하였으며,  $V_{ID}$  와  $V_{IF}$ 는 각각 직접 경로에서의 인풋과 피드포워드 경로에서의 인풋을 나타내고  $R_{EQ}$  와  $C_{EQ}$ 는 아웃풋 등가 저항과 등가 캐패시턴스이다. 이 값들은  $R_{EQ} = R/(1+\alpha)$ ,  $C_{EQ} = C(1+\alpha)$ 로 표현가능하며, 여기에서 R과 C는 직접 경로의 아웃풋 저항과 캐패시턴스이다. 결국 피드포워드 경로가 추가가 된다고 해도, 시간상수는  $R_{EQ}C_{EQ}$ 는 기존의 시간상수 RC와 같게 됨을 알 수 있다.

그림 3. (a) 기본 지연 스테이지의 소신호 등가회로 (b) 기본 지연 스테이지의 위상 도메인에서의 주 파수 응답

Fig. 3. (a) Small signal equivalent circuit of the unit stage

(b) Frequency response of the unit stage in phase domain

중첩의 원리를 이용하여 지연 스테이지의 주파수 응답을 구할 수 있다.  $V_{ID}$  와  $V_{IF}$  는 같은 전압 크기  $|V_{ID}|$ 를 가지며, 일정한 위상 차이  $\theta$  를 가지므로, 아래와 같은 전달 함수를 구할 수 있다.

$$\begin{split} V_{OUT} &= V_{OUT,ID} + V_{OUT,IF} \\ &= \frac{gmR_{EQ}(1 + \alpha \angle \theta)}{1 + jw_0RC} V_{ID} = H(\alpha) V_{ID} \end{split} \tag{2}$$

여기서  $H(\alpha)$  는 식 (3)을 의미하며,  $A=1+\alpha\cos(\theta)$ , 그리고  $B=\alpha\sin(\theta)$ 를 각각 의미한다.

$$H(\alpha) = \frac{gm(A+jB)R_{EQ}}{1+jw_0RC}$$

(3)

식 (3)을 통해서 피드포워드 링 오실레이터의 지연스테이지는 기존의 주파수 의존적인 위상 변화  $-\tan^{-1}(w_0RC)$ 에 주파수 독립적인 위상 변화  $\tan^{-1}(B/A)$  가 더해진 형태로 위상 변화량이 결정된다. 그림 3(b)는 위상 도메인에서 지연 스테이지의 주파수 응답을 표현한 것이다.  $\varphi$  와  $\psi$  은 각각 주파수 독립적인 위상 변화와 주파수 의존적인 위상 변화를 나타낸다. 지연 스테이지의 위상 변화량을  $\theta$ 로 두고  $w_0RC$ 를 구해보면,

$$w_0 RC = \tan \left[ \pi - \tan^{-1} (B/A) - \theta \right],$$

(4)

$0 < \phi = \pi - \tan^{-1} (B/A) - \theta < \pi/2$

가 된다는 것을 알 수 있다.  $\varphi$  에 대한 조건은  $w_0>0$  이 되기 위한 조건이다. 식(3)에 식(4)를 넣어서 전압 크기  $|H(\alpha)|$  에 대한 식을 구해보면,

나. 발진 주파수와 지배적인 mode 와의 관계 식(4)를 이용해서 발진 주파수를 계산해보면 식(6) 과 같다.

$$f_{osc} = -\frac{\sin(\theta) + \alpha \sin(2\theta)}{2\pi RC[\cos(\theta) + \alpha \cos(2\theta)]}$$

(6)

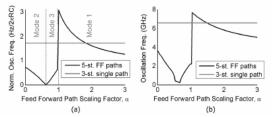

그림 4(a)는 4(6) 이용하여 계산한 피드포워드 경로의 크기비율  $\alpha$ 와  $2\pi$ RC 로 표준화한 발진 주파수와의 관계이다.

그림 4. (a) 예상되는 지배적인 mode와 발진주파수 (b) 발진주파수에 대한 시뮬레이션 결과

Fig. 4. (a) Predicted dominant mode and the oscillation frequency

(b) oscillation frequency simulation result

피드포워드 링 오실레이터는  $\alpha$ 에 따라서 발진하는

mode가 달라지며,  $0 < \alpha < 0.6$ 에서는 기존 링 오실레이터의 동작 mode인 mode 2에서,  $0.6 < \alpha < 1$ 에서는 mode 3에서, 그리고  $\alpha > 1$ 이면 mode 1에서 동작한다.

가장 높은 발진 주파수는 mode 1에서 발견되며, 특히 mode 1에서 발진하게끔 하는  $\alpha$ 의 범위 중에서  $\alpha$ 가 작아지면 작아질수록 더 높은 발진 주파수를 보인다.  $\alpha$ 가 mode 1에서 동작하도록 하는 범위 내에서 가장 작아지면, 3개의 지연 스테이지를 가지는 기존방식의 링 오실레이터보다 더 높은 발진 주파수를 보인다.

그림 4(b)는 0.18 m CMOS 공정을 사용하여 얻은 시뮬레이션 결과이다. 수학적인 예측과 일치함을 알 수 있다.

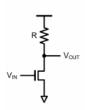

### 다. 발진 주파수의 최적화

지금까지의 시뮬레이션 및 수식적인 결과는 지연스테이지로 인버터를 사용하였다. 하지만, 인버터는 보통 전압이득이 20이상으로, 발진 조건인 전압이득 1을 훨씬 웃도는 전압이득을 가진다. 이는 곧 인버터와 같이 높은 전압이득을 가지는 지연 스테이지 대신에 전압이득은 낮더라도 더 넓은 대역폭을 가지는 지연 스테이지 대를 사용하면, 지금까지 계산된 발진주파수보다 더 높은 발진 주파수를 얻을 수 있다는 것을 의미한다.

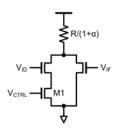

따라서 그림 5와 같이 부하저항을 사용하는 간단한 반전증폭기를 지연 스테이지로 사용하는 링 오실레이터 를 만들어 발진 주파수를 최적화 할 수 있다. NMOS 의 크기는 1 $\mu$ m 의 width 와 0.18 $\mu$ m 의 gate length를 가지게끔 설계하였다.

그림 5. 부하저항을 사용하는 반전증폭기 Fig. 5. A resistor loaded inverting amplifier

최적화는 오실레이터를 mode 1에서 동작하게 하는 가장 작은  $\alpha$  값  $(\alpha_{\min})$  을 찾음으로써 간단하게 진행할 수 있다. 식(7)은 식(5)를 사용하여, 주어진 부하저항에 따른  $\alpha_{\min}$ 을 수식적으로 구한 결과이다.

$lpha_{\min}(R) = -\left[1 + A_{dc}\cos\left( heta

ight)\right]/\left[1 + A_{dc}\cos\left(2 heta

ight)\right]$  (7) 여기에서  $A_{dc}$ 는 지연 스테이지의 전압이득이며, heta 의 경우 mode 1에서 동작하기를 원하므로  $2\pi/5$ 로 정

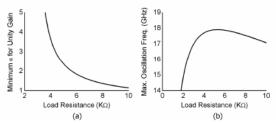

한다. 이렇게 하여 계산된 부하저항에 따른  $\alpha_{\min}$ 은 그림 6(a)와 같다. 그림 6(b)는 각 부하저항에 따른 오실 레이터가 가질 수 있는 최대 발진주파수에 대한 시뮬레이션 결과이다. 부하저항이  $5k\Omega$  정도 되면, 17대한 라는  $0.18\mu$ 에의 공정으로는 눈에 띌만한 높은 발진주파수를 가지는 링 오실레이터를 만들 수 있다.

- 그림 6. (a) 부하저항에 따른  $lpha_{\min}$  값

- (b) 부하저항에 따른 최고 발진주파수

Fig. 6. (a)  $\alpha_{\rm m\,in}$  for unity unit stage gain (b) Maximum oscillation frequency as a function of R

## Ⅲ. 실 험

실제 칩 제작에 사용한 지연 스테이지의 구조는 최대한 간단히 집적화하기 위해서 그림 7과 같이 하나의 지연 스테이지 직접 경로와 피드포워드 경로를 한꺼번에 가지는 구조로 결정했다.

그림 7. 피드포워드 링 오실레이터의 지연 스테이지 Fig. 7. Delay stage of feed forward ring oscillator

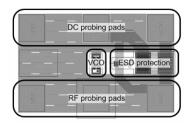

0.18- $\mu$ m CMOS 공정을 이용하여 레이아웃 된 칩의 모습은 그림 8과 같으며, 1.8V 공급전압을 사용하였고, 패드와 ESD보호회로를 제외한 실제 칩 면적은  $0.001mm^2$  이하이다.

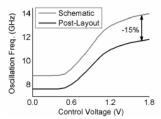

위의 칩의 발진 주파수에 대한 시뮬레이션 결과는 그림 9와 같다. 스케메틱 시뮬레이션과 포스트레이아웃 시뮬레이션 결과는 15% 정도의 차이를 보이며, 포스트레이아웃 시뮬레이션 결과 최고 발진 주파수는 12GHz 정도로, 0.18- $\mu$ m 공정으로는 보고된 적이 없을 정도로 높은 발진 주파수를 가진다.

그림 8. 피드포워드 링 오실레이터 레이아웃 Fig. 8. Layout of the feed forward ring oscillator

그림 9. 피드포워드 링 오실레이터 발진주파수 시뮬레이 션 결과

Fig. 9. Post layout simulation of feed forward ring oscillator

# Ⅳ. 결 론

피드포워드 방식 링 오실레이터에 대한 새로운 모델을 제시하였고, 특성에 대한 분석을 하였다. 피드포워드 경로의 비중 조절을 통해서 최고 속도의 발진 주파수를 얻을 수 있는 방법 또한 제시하였다.  $0.18-\mu$ m 공정을 이용한 포스트 레이아웃 시뮬레이션 결과 12GHz 에육박하는 발진 주파수를 얻어냈다.

## 참 고 문 헌

- [1] Chan-Hong Park, and Beomsup Kim, "A low-noise, 900-MHz VCO in 0.6-\mu CMOS", IEEE J. Solid-Stage Circuits, vol.34, no. 5, pp.586-591, May 1999

- [2] Dean A. Badillo and Sayfe Kiaei, " A low phase noise 2.0V 900MHz CMOS voltage controlled ring oscillator", in proc. IEEE Int. Symp. Circuits Syst.(ISCAS'04), vol. 4, pp. 533-536, 2004

- [3] Hai Qi Liu, Wang Ling Goh and Liter Siek, "0.18-\mu 10-G\mu CMOS ring oscillator for optical transceivers", in proc. IEEE Int. Symp. Circuits Syst.(ISCAS'05), vol. 4, pp.1525-1528, 2005.