# An Asymmetrically-Sampling 10-Gb/s CDR Circuit for Optical Receiver Performance Enhancement

Dae-Hyun Kwon, Hyun-Yong Jung, Jeong-Min Lee, and Woo-Young Choi Department of Electrical and Electronic Engineering Yonsei University Seoul, Korea wchoi@yonsei.ac.kr

#### Abstract

We demonstrate a new type of optical receiver that contains a clock and data recovery (CDR) circuit having asymmetric samplers for electronicphotonic integrated circuit applications. The CDR directly samples pseudo-differential signals provided by the transimpedance amplifier (TIA) without any need for offset cancellation. This results in the reduction of the optical receiver power consumption and chip area. An optical receiver containing an equivalent circuit for the photodetector, TIA, and asymmetrically sampling CDR is implemented in 65nm CMOS technology and the measurement results confirm the advantage of our new structure.

**Keywords:** Clock and Data Recovery (CDR); Electronic and Photonic Integrated Circuits (EPIC); Optical Receiver; Transimpedance Amplifier (TIA)

## 1. Introduction

There are a great amount of research and development interests for optical interconnect technology as the need for higher-bandwidth serial interfaces is continuously increasing and the conventional electrical interconnect technology is facing serious bandwidth, power, and footprint limitations. Furthermore, it is now possible to realize electronic and photonic integrated circuits (EPICs) for optical interconnect applications as photonic devices can be realized on Si platform with the Si processing technology [1, 2]. For successful implementation of Si EPICs, high-performance Si photonic devices are needed along with high-speed, power-efficient analog front-end circuits such as modulator drivers and transimpedance amplifiers (TIAs). Furthermore, serializer/deserializer (SerDes) circuits should be implemented in such a way that they are optimized for the target optical interconnect applications.

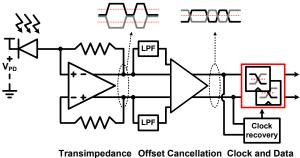

Transimpedance Offset Cancellation Clock and Data Amplifier Network Recovery Fig. 1. Block diagram of conventional optical receiver.

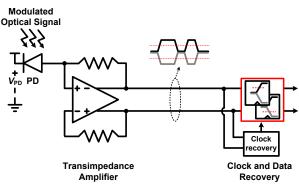

Fig. 2. Block diagram of proposed optical receiver.

Fig. 1 shows the architecture of the conventional optical receiver that includes a photodetector (PD), TIA, offset cancellation network (OCN), and a clock and data recovery (CDR) circuit [3]. A limiting amplifier is not included here since for optical interconnect applications TIA alone can provide sufficient signal levels required by CDR. For the high-speed operation required for the optical interconnect applications, differential-type TIA is preferred. However, since received optical signals are singled-ended, the PD provides single-ended signals to TIA. Consequently, an OCN [4, 5] is needed, which cancels the DC offset and converts pseudo-differential signals to fully differential signals for CDR as shown in Fig. 1. However, OCN should

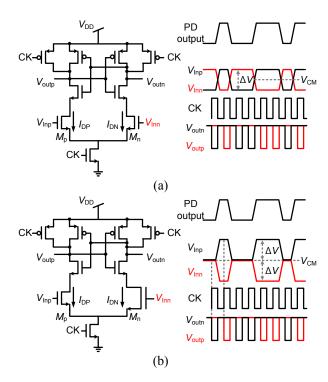

Fig. 3. Schematics of the sense-amplifier for (a) symmetric and (b) asymmetric sampler.

have a lower cutoff frequency to avoid the timedomain "droop" problem [6], which requires large resistance and capacitance, resulting in increased chip area. In addition, the OCN consumes a significant amount of power as it has to provide sufficient bandwidth. In this paper, we propose a novel architecture that allows the elimination of OCN. As shown in Fig. 2, the proposed architecture is based on CDR with an asymmetric sampler that can directly sample pseudo-differential signals provided by TIA with different decision thresholds for each of two differential input pairs. We demonstrate that such CDR can provide enhanced optical receiver performance in terms of power consumption and chip area.

## 2. Optical Receiver Circuits

A sense amplifier [8] (SA) is used for the CDR sampler since it has advantages in power consumption and sensitivity. In addition, it can be easily analyzed when DC voltages are applied to differential input pairs [9]. In the conventional SA as shown in Fig. 3(a), the sampler is pre-charged to  $V_{DD}$  when the clock is off, and it discharges the currents corresponding to the input voltage level when the clock is on. Current imbalance caused by the input voltage level difference results in different output levels, which with the positive feedback produces the desired output. These SA characteristics can be used for sampling pseudo-differential signals by making

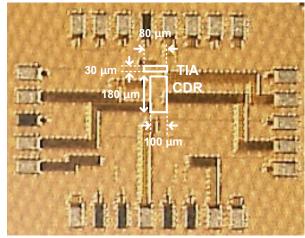

Fig. 4. Chip microphotograph of optical receiver with asymmetrically-sampling CDR.

the sizes of input MOSs different.

In Fig. 3(b), the size of  $M_n (=W_n/L_n)$  should be larger than that of  $M_p (=W_p/L_p)$  while  $W_p \times L_p = W_n \times L_n$ is maintained so that two inputs provide the same load capacitance to the TIA. When there is no input light, the pseudo-differential input signals have the same voltage level. In this case,  $V_{outn}$  is discharged to ground when the clock is on, because  $I_{DN}$  is larger than  $I_{DP}$ . When there is input light, the pseudodifferential input signals have difference of  $2\Delta V$ . In this case, the discharged output should be  $V_{outp}$  rather than  $V_{outn}$  in order to avoid any errors. This requires  $I_{DP}$  larger than  $I_{DN}$ .

$$I_{\rm DP} > I_{\rm DN} \tag{1}$$

where

$$I_{\rm DP} = \frac{1}{2} \,\mu_{\rm n} C_{\rm OX} \,\frac{W_{\rm p}}{L_{\rm n}} \left( V_{\rm GS,M_{\rm P}} - V_{\rm TH,M_{\rm P}} \right)^2$$

(2)

and

$$I_{\rm DN} = \frac{1}{2} \mu_{\rm n} C_{\rm OX} \frac{W_{\rm n}}{L_{\rm n}} (V_{\rm GS,M_{\rm n}} - V_{\rm TH,M_{\rm n}})^2$$

(3)

Substituting Eq. (2) and (3) into Eq. (1),

$$\frac{W_{\rm p} \times L_{\rm n}}{L_{\rm p} \times W_{\rm n}} > \frac{\left(V_{\rm CM} - V_{\rm S} - \Delta V - V_{\rm TH,M_{\rm n}}\right)^2}{\left(V_{\rm CM} - V_{\rm S} + \Delta V - V_{\rm TH,M_{\rm p}}\right)^2} \,. \tag{4}$$

With Eq. (4), we can determine input MOS sizes for target  $\Delta V$ .

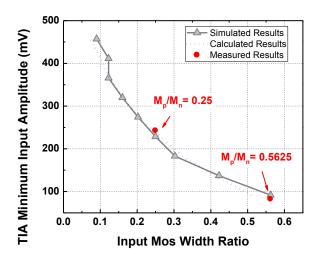

10-Gbps optical receivers having quarter-rate CDR with two different asymmetric samplers satisfying Eq. (4) are designed in 65-nm CMOS technology. One sampler has  $M_p/M_n$  ratio of 0.5625, or  $W_p/L_p=7.5 \ \mu\text{m}/80 \ \text{nm}$  and  $W_n/L_n=10 \ \mu\text{m}/60 \ \text{nm}$ , and the other sampler has  $M_p/M_n$  ratio of 0.25, or  $W_p/L_p=5 \ \mu\text{m}/120 \ \text{nm}$  and  $W_n/L_n=10 \ \mu\text{m}/60 \ \text{nm}$ . Both optical receivers contain an identical TIA which

Fig. 5. Measurement setup for optical receiver.

Fig. 6. Input sensitivity of proposed optical receiver with simulation and calculation results.

employs the shunt-feedback topology [7] and the equivalent circuit for the photodetector consisting of 30-fF capacitor and 2-k $\Omega$  resistor along with 50- $\Omega$  termination resistor needed for measurement.

#### **3. Measurement Results**

Fig. 4 shows the microphotograph of the fabricated optical receiver. The TIA core area is 0.0024 mm<sup>2</sup> (30  $\mu$ m×80  $\mu$ m) and that of CDR is 0.018 mm<sup>2</sup> (100  $\mu$ m×180  $\mu$ m).

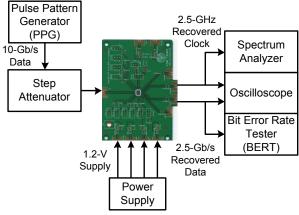

Fig. 5 shows the measurement setup for evaluating the optical receiver circuit performance. The fabricated chip is mounted on printed circuit board (PCB) and wire bonded. A pulse pattern generator (PPG) provides 10-Gb/s 2<sup>7</sup>-1 PRBS patterns to the optical receiver. Spectrum analyzer and oscilloscope are used to measure the recovered clock and data. Bit error rate tester (BERT) is used to confirm the CDR does not generate any error.

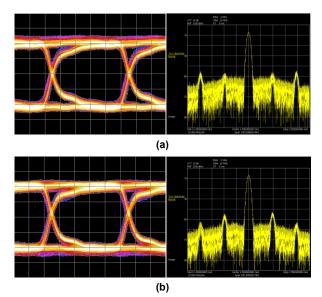

Fig. 7. (a)  $M_p/M_n=0.5625$  and (b)  $M_p/M_n=0.25$ , 2.5-Gb/s retimed data eye-diagram and 2.5-GHz retimed clock spectrum.

**Table 1: Performance summary**

| Data-rate [Gb/s]                       | 10                                               |

|----------------------------------------|--------------------------------------------------|

| Receiver<br>architecture               | PD model + TIA + CDR                             |

| Power consumption<br>[mW]              | 10 (CDR core)<br>10 (VCO)<br>8 (TIA)             |

| TIA minimum<br>input amplitude<br>[mV] | 82 $(M_p/M_n=0.5625)$<br>242 $(M_p/M_n=0.25)$    |

| Jitter of retimed<br>data (RMS) [ps]   | 8.19 $(M_p/M_n=0.5625)$<br>7.56 $(M_p/M_n=0.25)$ |

| Area [mm <sup>2</sup> ]                | 0.0024 (TIA)<br>0.018 (CDR)                      |

Fig. 6 shows the measured minimum TIA input voltages for optical receivers having two different samplers when the BER is less than  $10^{-12}$ . SPICE simulation and calculated results based on Eq. (4) are also shown in Fig. 6. Measured results agree very well with the simulated and calculated results.

Fig. 7 shows the measured retimed data eyediagrams and retimed clock spectra for CDRs having two different samplers. Table I summarizes the performance of our circuit. In order to determine how much power consumption and chip-area is reduced with our new structure, we also designed OCN used for 10-Gbps optical receiver with symmetrically sampling CDR in the same 65-nm CMOS technology. The designed OCN consumes 5 mW and its area is 0.002 mm<sup>2</sup>. This indicates that our new structure provides roughly 15% power and 9% area reduction.

The slight difference in measured jitter characteristics is due to the difference in loop gain for two types of CDR circuits caused by different input amplitudes.

## 4. Conclusion

A 10-Gb/s optical receiver circuit with asymmetrically sampling CDR is demonstrated in 65nm CMOS technology. Our optical receiver circuit can directly sample pseudo-differential signals provided by TIA, resulting in reduced power consumption and chip area.

#### Acknowledgments

This work was supported by the National Research Foundation of Korea grant funded by the Korea government (MEST) [NRF-2015R1A2A2A01007772]. The authors are also thankful to IDEC for MPW and EDA software support.

## References

[1] J. F. Buckwalter, X. Zheng, G. Li, K. Raj, and A. V. Krishnamoorthy, "A Monolithic 25-Gb/s transceiver with Photonic Ring Modulators and Ge Detectors in a 130-nm CMOS SOI Process," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 6, pp. 1309–1322, June 2012.

[2] J. Kim and J. F. Buckwalter, "A 40-Gb/s Optical Transceiver Front-End in 45nm SOI CMOS," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 3, pp. 348–352, May 2010.

[3] B. Razavi, Design of Integrated Circuits for Optical Communications, 1st ed. New York, NY, USA: McGraw Hill, 2002.

[4] S. Huang and W.-Z. Chen, "A 20-Gb/s Optical Receiver with Integrated Photo Detector in 40-nm CMOS", *IEEE Asian Solid-State Circuit Conference*, pp. 225–228, Nov. 2013.

[5] D.-W. Kim, H.-K. Choi, Y.-S. Chun, M.-H. Chin, G. Kim, and D.-K. Jeong, "12.5-Gb/s Analog Front-End of an Optical Transceiver in 0.13-µm CMOS," *IEEE International Symposium on Circuits and Systems*, pp. 1115–1118, 2013.

[6] S. Galal and B. Razavi, "10-Gb/s Limiting Amplifier and Laser/Modulator Driver in 0.18-μm CMOS Technology," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2003.

[7] E. Säckinger, "The Transimpedance Limit," *IEEE Transactions on Circuits and Systems-I: Regular Papers*, vol. 57, no. 8, pp. 1848–1856, Aug. 2010.

[8] T. Kobayashi, K. Nogami, T. Shirotori, and Y. Fujimoto, "A Current-Contolled Latch Sense Amplifier and a Static Power-Saving Input Buffer for Low-Power Architecture," *IEEE Journal of Solid-State Circuits*, vol. 28, pp. 523–527, Apr. 1993.

[9] B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and Speed Optimization of a Latch-Type Voltage Sense Amplifier", *IEEE Journal of Solid-State Circuits*, vol. 39, no. 7, pp. 1148–1158, July 2004.