http://www.iceic.org

International Conference on Electronics, Information, and Communication 2024

Jan. 28(SUN) - 31(WED) 2024 Taipei Marriott Hotel, Taiwan

# **ICEIC**

International Conference on Electronics, 2024 Information, and Communication 2024

### **CONTENTS**

| 01. Welcome | to ICEIC 2024 |

|-------------|---------------|

|-------------|---------------|

02. Technical Program Overview

### 03. Committee

- Organizing Committee

- Technical Program Committee

04. Time Table

05. Floor Map

### 06. Conference Information

- Social Program 12 - Registration 13

10

16

19

21

26

- Presentation Guidelines 15

07. Plenary Talks

08. Invited Talk

09. Tutorials

10. Technical Program

- Oral Sessions 26 53 - Poster Sessions

11. Venue & Accommodation 78

12. About Taiwan 79

## Time Table

### Sunday, January 28, 2024

| Time        | Garden<br>Villa (8F)               | Junior<br>Ballroom I (5F) | Junior<br>Ballroom II (5F) | Fortune Room<br>(5F) | Prosperity<br>Room (5F) | Longevity<br>Room (5F) | Lobby<br>(5F) |

|-------------|------------------------------------|---------------------------|----------------------------|----------------------|-------------------------|------------------------|---------------|

| 15:00~16:30 | P-16:30 Registration (Lobby (1F))  |                           |                            |                      |                         |                        |               |

| 17:30~      | Welcome Reception (Ballroom (37F)) |                           |                            |                      |                         |                        |               |

### Monday, January 29, 2024

| Time        | Garden<br>Villa (8F)                                                                                           | Junior<br>Ballroom I (5F)                          | Junior<br>Ballroom II (5F)                                                                              | Fortune Room<br>(5F)                                                                                                                      | Prosperity<br>Room (5F)                                           | Longevity<br>Room (5F)                          | Lobby<br>(5F)                                                                  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| 08:30~16:30 | Registration (Lobby (5F))                                                                                      |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 09:00~10:15 |                                                                                                                | Tutorial 1<br>Prof. Itaru Kitahara                 | SS1<br>Novel High-Speed and<br>Low-Power Memory<br>Technology <mark>(Invited)</mark>                    | OS1<br>System and Control (1)                                                                                                             | OS2<br>Artificial<br>Intelligence and<br>Signal<br>Processing (1) | OS3<br>Semiconductor<br>Devices/Circuits<br>(1) | Poster Session 1<br>Artificial<br>Intelligence and<br>Signal Processing<br>(1) |  |  |  |  |

| 10:15~10:20 |                                                                                                                | Break Time                                         |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 10:20~10:30 | Opening Ceremony (Garden Villa (8F))                                                                           |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 10:30~11:05 | Plenary Talk 1 (Garden Villa (8F)): Dr. Michael Shebanow (CTO of SAPEON Inc.)                                  |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 11:05~11:40 | Plenary Talk 2 (Garden Villa (8F)): Prof. Ching-Ting Lee (National Cheng Kung University / Yuan Ze University) |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 11:40~13:00 | Lunch (Exhibit Hall (3F))                                                                                      |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 13:00~14:15 |                                                                                                                | Tutorial 2<br>Prof. Hansung Kim                    | SS2<br>Software Aspects and<br>Possible Future<br>Applications of<br>Processing-in-<br>Memory Technique | SS3<br>Multidisciplinary<br>Research Training and<br>Development<br>Enterprise for Al and<br>Semiconductor<br>Technology (1)<br>(Invited) | OS4<br>Artificial<br>Intelligence and<br>Signal<br>Processing (2) | OS5<br>Semiconductor<br>Devices/Circuits<br>(2) | Poster Session 2<br>Artificial<br>Intelligence and<br>Signal Processing<br>(2) |  |  |  |  |

| 14:15~15:30 |                                                                                                                | SS4<br>Next generation<br>multimedia<br>processing | SS5<br>Novel Devices and<br>Circuits for Advanced<br>Computing<br>Technologies (1)<br>(Invited)         | SS6<br>Multidisciplinary<br>Research Training and<br>Development<br>Enterprise for Al and<br>Semiconductor<br>Technology (2)<br>(Invited) | OS6<br>Communications<br>(1)                                      | OS7<br>Semiconductor<br>Devices/Circuits<br>(3) | Poster Session 3<br>Artificial<br>Intelligence and<br>Signal Processing<br>(3) |  |  |  |  |

| 15:30~15:45 | Coffee Break                                                                                                   |                                                    |                                                                                                         |                                                                                                                                           |                                                                   |                                                 |                                                                                |  |  |  |  |

| 15:45~17:00 |                                                                                                                | SS7<br>Applied Al @<br>SeoulTech<br>(Invited)      | SS8 Novel Devices and Circuits for Advanced Computing Technologies (2) (Invited)                        | SS9<br>Multidisciplinary<br>Research Training and<br>Development<br>Enterprise for Al and<br>Semiconductor<br>Technology (3)<br>(Invited) | OS8<br>Communications<br>(2)                                      | OS9<br>Computer and<br>Information (1)          | Poster Session 4<br>Computer and<br>Information &<br>Emerging<br>Technologies  |  |  |  |  |

### Tuesday, January 30, 2024

| Time        | Garden     | Junior                                  | Junior                                                                                              | Fortune Room                                                                                                                                       | Prosperity                                                         | Longevity                                        | Lobby                                                          |  |  |  |  |

|-------------|------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| Time        | Villa (8F) | Ballroom I (5F)                         | Ballroom II (5F)                                                                                    | (5F)                                                                                                                                               | Room (5F)                                                          | Room (5F)                                        | (5F)                                                           |  |  |  |  |

| 09:00~16:30 |            |                                         | Reg                                                                                                 | istration (Lobby (5F                                                                                                                               | ))                                                                 |                                                  |                                                                |  |  |  |  |

| 09:30~10:45 |            | OS10<br>System and Control<br>(2)       | SS10<br>High-speed<br>wireline IO<br>(Invited)                                                      | SS11<br>Future Brain-Inspired<br>Intelligence System<br>Semiconductor                                                                              | OS11<br>Communica-<br>tions (3)                                    | OS12<br>Semiconductor<br>Devices/Circuits<br>(4) | Poster Session 5<br>Semiconductor<br>Devices/Circuits (1)      |  |  |  |  |

| 10:45~10:55 |            | Break Time                              |                                                                                                     |                                                                                                                                                    |                                                                    |                                                  |                                                                |  |  |  |  |

| 10:55~11:30 | Invited    | d Talk (Junior Ballro                   | om I (5F)) : Prof. Dr                                                                               | Ing. Nilesh Madhu (IC                                                                                                                              | Lab / Ghent Univ                                                   | versity)                                         |                                                                |  |  |  |  |

| 11:30~13:00 |            |                                         | Lunch                                                                                               | n (Garden Kitchen (1                                                                                                                               | F))                                                                |                                                  |                                                                |  |  |  |  |

| 13:00~14:15 |            | Tutorial 3<br>Dr. Sungho Suh            | SS12 Recent Progresses in Electronic and Electrical Engineering at Ewha Womans University (Invited) | SS13 Exploring Cutting— Edge Technologies for Electronic Devices and Signal Processing — Yonsei University and Chang—Gung University Joint Session | OS13<br>Artificial<br>Intelligence and<br>Signal<br>Processing (3) | OS14<br>Semiconductor<br>Devices/Circuits<br>(5) | Poster Session 6<br>Semiconductor<br>Devices/Circuits (2)      |  |  |  |  |

| 14:15~15:30 |            | Tutorial 4<br>Mr. Chaeun Lee            | SS14 Next-Generation Intelligent Mobility Platforms @ SeoulTech (Invited)                           | SS15<br>Charge-Trap Memory,<br>Circuits, and Systems<br>for Hardware On-Chip<br>Learning (Invited)                                                 | OS15<br>Artificial<br>Intelligence and<br>Signal<br>Processing (4) | OS16<br>Emerging<br>Technologies (1)             | Poster Session 7<br>Semiconductor<br>Devices/Circuits (3)      |  |  |  |  |

| 15:30~15:45 |            | Coffee Break                            |                                                                                                     |                                                                                                                                                    |                                                                    |                                                  |                                                                |  |  |  |  |

| 15:45~17:00 |            | OS17<br>Computer and<br>Information (2) | SS16 Development for Processing Software on Al Semiconductor Devices @ SeoulTech                    | SS17<br>i-EoT System IC<br>(Invited)                                                                                                               | OS18<br>Artificial<br>Intelligence and<br>Signal<br>Processing (5) | OS19<br>Emerging<br>Technologies (2)             | Poster Session 8<br>Communications &<br>Systems and<br>Control |  |  |  |  |

| 18:00~      |            |                                         | Banq                                                                                                | uet (Garden Villa (8                                                                                                                               | F))                                                                |                                                  |                                                                |  |  |  |  |

|             |            |                                         |                                                                                                     |                                                                                                                                                    |                                                                    |                                                  |                                                                |  |  |  |  |

### Wednesday, January 31, 2024

| Time             | Garden<br>Villa (8F)                                                   | Junior<br>Ballroom I (5F) | Junior<br>Ballroom II (5F) |  | Prosperity Room<br>(5F) | Longevity Room<br>(5F)                                                                                             | Lobby<br>(5F) |

|------------------|------------------------------------------------------------------------|---------------------------|----------------------------|--|-------------------------|--------------------------------------------------------------------------------------------------------------------|---------------|

| 09:30 -<br>10:30 | ICEIC Committee Meeting / Closing Ceremony (Organizing Committee Only) |                           |                            |  |                         | SEOULTECH LINC 3.0:<br>Industry-Academic<br>Cooperation Matching<br>Day for Multidisciplinary<br>Research Training | ÷             |

### ICEIC2024

### International Conference on Electronics. Information, and Communication 2024

### Artificial Intelligence and Signal Processing (1)

09:00~10:15

Monday, January 29, 2024

Prosperity Room (5F)

Chair: Hyunmin Jung (SEOULTECH)

### <sup>01</sup> Mental Health Identification Through Face Emotion Recognition Using Machine Learning

Dr.N. Magadevi<sup>1</sup> and M. Indumathi<sup>2</sup>

<sup>1</sup>S.A. Engineering College, India, <sup>2</sup>Jeppiaar Institute Of Technology, India

#### O2 Detection of Circulating Tumor Cells in Blood Using Random Forest

Hua Wei<sup>1</sup>, Takahiro Natori<sup>2</sup>, Tomohiro Tanaka<sup>3</sup>, Shin Aoki<sup>1</sup>, Takeshi Yamada<sup>4</sup>, and Naoyuki Aikawa<sup>1</sup> <sup>1</sup>Tokyo University of Science, Japan, <sup>2</sup>Tokai University, Japan, <sup>3</sup>Okayama University, Japan, <sup>4</sup>Nippon Medical School, Japan

### 03 Vehicle-to-Vehicle Communication Channel Estimator Based on Gate Recurrent Unit

Jun-Han Wang<sup>1</sup>, He He<sup>1</sup>, Kosuke Tamura<sup>1</sup>, Shun Kojima<sup>2</sup>, Jaesang Cha<sup>1</sup>, and Chang-Jun Ahn<sup>1</sup> <sup>1</sup>Chiba University, Japan, <sup>2</sup>The University of Tokyo, Japan

#### <sup>04</sup> Serial Skeletal Detection using a Kalman Filter in Combination with OpenPose

Sota Sugiyama, Masataka Yamamoto, Hiroshi Takemura, and Naoyuki Aikawa Tokyo University of Science, Japan

### <sup>05</sup> Improved Generalization from Limiting Attention in a Transformer for Sleep Stage Classification

Dongyoung Kim, Dong-Kyu Kim, and Jeong-Gun Lee Hallym University, Korea

### Semiconductor Devices/Circuits (1)

09:00~10:15

Monday, January 29, 2024

Longevity Room (5F)

Chair: Hoyoung Yoo (Chungnam National University)

### <sup>01</sup> A Current Mirror Based Read Circuit Design with Multi-Level Capability for Resistive **Switching Devices**

Stefan Pechmann<sup>1</sup>, Eduardo Perez<sup>2,3</sup>, Christian Wenger<sup>2,3</sup>, and Amelie Hagelauer<sup>1,4</sup> <sup>1</sup>Technical University of Munich, Germany, <sup>2</sup>IHP, Germany, <sup>3</sup>Brandenburg University of Technology, Germany, <sup>4</sup>Fraunhofer EMFT, Germany

### 02 Thermal Shutdown implementation in BLE microcontroller for TPMS and Industrial

Aritra Chowdhury and Venkatesh G. Kadlimatti Texas Instruments (India) Pvt. Ltd., India

### <sup>03</sup> Low-power, 25-Gb/s Active Voltage Current Feedback Transimpedance Amplifier in 65-nm CMOS

Koji Tominaga and Yasuhiro Takahashi Gifu University, Japan

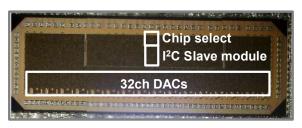

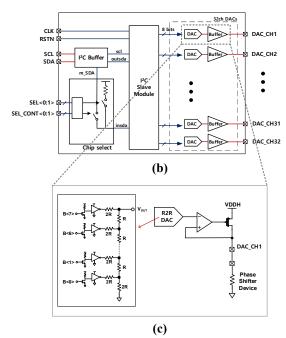

### 04 A 32-channel DAC-based Driver IC for Optical Phased Array

Kihun Kim and Woo-Young Choi Yonsei University, Korea

### <sup>05</sup> Physical Unclonable Function using Programmable Delay Lines

Jiho Park, Heehun Yang, Donghun Lee, and Hoyoung Yoo Chungnam National University, Korea

### Software Aspects and Possible Future Applications of Processing-in-Memory Technique

13:00~14:15

Monday, January 29, 2024

Junior Ballroom II (5F) Chair: Kyuhyun Choi (KETI)

### <sup>01</sup> Building an Inference Server Platform for Large Language Models Using Dataflow PIM Platform

Kyu Hyun Choi and Taeho Hwang KETI. Korea

### 02 Supporting Multi-Channels to DRAM-based PIM Execution for Boosting the Performance

Junil Kim, Seok Young Kim, and Seon Wook Kim

Korea University, Korea

### 03 Low Overhead PIM-to-PIM Communication on PCIe-based Multi-PIM Platforms for Executing Large-Scale Al Models

Mun Seong Park, Seok Young Kim, and Seon Wook Kim Korea University, Korea

### A 32-channel DAC-based Driver IC for Optical Phased Array

### Kihun Kim<sup>1\*</sup>, and Woo-Young Choi<sup>1</sup>

Department of Electrical & Electronic Engineering, Yonsei University, Seoul, South Korea<sup>1</sup>

\*khkim511@yonsei.ac.kr

### **Abstract**

This paper presents a 32-channel Optical Phased Array (OPA) driver IC for LiDAR application. The OPA, based on Silicon Photonics, offers precise beamforming and steering. The driver IC achieves 5.26° resolution with a fabricated Si Mach-Zehnder Interferometer, demonstrating it can be used for 32-channel OPAs.

Keywords: Driver IC, OPA

### 1. Introduction

Recently, the autonomous driving technology has been attracting a significant amount of attention and intensive R&D activities are being carried out for Light Detection, and Ranging (LiDAR), a key sensing element expected to be essential for selfdriving cars. LiDAR takes the advantage of light, which has over 1000 times shorter wavelength than the electromagnetic waves used RADAR. This results in the much higher resolution and the directionality. The beamforming and the beam steering can be realized with the mechanical rotating method, but this approach results in bulky systems and reliability issues. In contrast, solid-state Optical Phased Array (OPA) based on the Si Photonics technology can achieve beam forming by an array of light-emitting elements that can be realized with grating couplers and beam steering by adjusting the phase difference between lightwaves delivered to the grating couplers. Moreover, the Si IC fabrication technology with which Si Photonic Integrated Circuits can be fabricated allows realization of smallfootprint devices with cost effectiveness.

There are two different methods for achieving phase shifting in OPA: Electro-optic (EO) modulation and thermo-optic (TO) modulation. EO modulation involves changing the effective index by applying the voltage signal to an optical phase shifter through which the light signal passes. It has the advantage of high modulation speed but the disadvantage of significant insertion loss. This makes it unsuitable for OPA in which the light signal from a

single source is divided into numerous channels. Consequently, in many OPA implementations [1-3], the slower but relatively low-loss TO modulation method is used, in which the effective index is changed by heating the optical phase shifter with onchip heaters. These heaters require electronic drivers that can supply proper heater voltages in order to realize the desired beam steering. In this paper, we report a 32-channel DAC(Digital-to-Analog Converter)-based OPA driver IC realized with 180nm CMOS technology.

### 2. OPA Driver IC

Fig. 1(a) and 1(b) show the microphotograph and the block diagram of the fabricated OPA driver IC. This IC delivers voltage signals to on-chip metal heaters within 32 optical phase shifters through 8-bit DAC. Desired DAC output signals levels are delivered from an external controller through I<sup>2</sup>C communication. The Chip Select function is built-in so that several driver ICs be used for OPAs having more than 32 array elements.

Fig. 1(c) shows the R2R ladder structure used for the DAC as well as the driver buffer. The R2R ladder structure has excellent linearity because it uses only two resistance values, R and 2R, and is widely adopted as a binary weighted DAC structure because of its simple design. Since the required maximum current for the target optical phase shifter in this research is quite large (~30mA), an amp and a large-sized PMOS are employed to build a unity gain buffer so that it can drive the metal heater with the voltage level identical to the output of the R2R ladder DAC.

Fig. 1 (a) Microphotograph and (b) Block diagram of OPA driver IC. (c) Schematic of R2R ladder DAC and buffer.

### 3. DAC measurement result

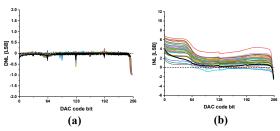

Fig. 2(a) and 2(b) show the measured DNL and INL of the driver IC for all 32 channels. The black solid lines in the figures are the simulation results. Typically, a good DAC should have both DNL.max and INL.max within 0.5 LSB (Least Significant Bit). However, in the measurement results, DNL.max is 0.99 LSB, and INL.max is 6.98 LSB. The larger INL values can be attributed to the voltage drop across the drain-source of the large-size PMOS and the limited operating range of the amplifier in the DAC's buffer stage. However, the DAC output is monotonic (DNL > -1 LSB) so that it can be used for OPA where the linearity of the DAC is relatively less critical because the voltage applied to the optical phase shifter and the resulting optical phase shift have a non-linear relationship in the TO method.

Fig. 2 (a) Measured DNL and (b) INL for all 32 channels of OPA driver IC.

### 4. Resolution of phase shifter

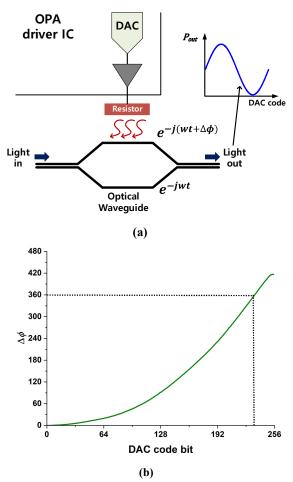

In order to demonstrate the fabricated driver IC can be used for OPA, a Si Mach-Zehnder Interferometer(MZI) is fabricated and its optical output is measured with different DAC output signals. As shown in Fig. 3(a), when the voltage signal provided by the DAC is applied to a resistor positioned directly above one of two optical waveguides having the nominally equal length, it results in increase in the temperature for the waveguide, changes its effective index, and causes the phase difference between lightwaves propagating in two different arms. This phase difference results in the output optical intensity change. The designed MZI (phase shifter) consumes 97.7mW for 360° phase shift. Moreover, the require voltage level is 3.01V, remaining well within the IC chip's high supply voltage(3.3V) range.

Fig. 3 (a) Thermo-optic phase modulation mechanism. (b) Measured phase variation of phase shifter.

Fig. 3(b) shows the phase shift as a function of the DAC code.  $\Delta \phi$  exhibits a square dependence on the DAC code since  $\Delta \phi$  is linearly related to heater

power, which is proportional to V<sup>2</sup>. The maximum phase difference measured for two adjacent DAC codes is 5.26°. With this, it is expected that beam steering with a 32-channel OPA can be achieved.

### 5. Acknowledgement

This research was supported by the Challengeable Future Defense Technology Research and Development Program through the ADD funded by DAPA in 2022 (No. 915027201). The EDA Tool was supported by the IC Design Education Center (IDEC).

### References

- [1] S. Chung, H. Abediasl, and H. Hashemi, "A monolithically integrated large-scale optical phased array in silicon-on-insulator CMOS.", *IEEE Journal of Solid-State Circuits*, vol. 53, no. 1, 275-296. January 2018.

- [2] R. Fatemi, A. Khachaturian, and A. Hajimiri, "A nonuniform sparse 2-D large-FOV optical phased array with a low-power PWM drive.", IEEE Journal of Solid-State Circuits, vol. 54, no. 5, 1200-1215. May 2019.

- [3] T. Kim, P. Bhargava, P. Poulton, ... and V. Stojanovic "A Single-Chip Optical Phased Array in a Wafer-Scale Silicon Photonics / CMOS 3D-Integration Platform.", IEEE Journal of Solid-State Circuits, vol. 54, no. 11, 3061-3074. November 2019.