## **PHOTONICS Research**

# Silicon electronic-photonic integrated 25 Gb/s ring modulator transmitter with a built-in temperature controller

MINKYU KIM,<sup>1</sup> Min-Hyeong KIM,<sup>1,2</sup> Youngkwan Jo,<sup>1</sup> Hyun-Kyu KIM,<sup>1</sup> Stefan Lischke,<sup>3</sup> Christian Mai,<sup>3</sup> Lars Zimmermann,<sup>3,4</sup> and Woo-Young Choi<sup>1,\*</sup>

<sup>1</sup>Department of Electrical and Electronic Engineering, Yonsei University, 03722 Seoul, Republic of Korea

Received 27 October 2020; revised 18 January 2021; accepted 2 February 2021; posted 2 February 2021 (Doc. ID 413407); published 22 March 2021

We demonstrate a silicon electronic-photonic integrated 25 Gb/s nonreturn-to-zero transmitter that includes driver circuits, depletion-type Si ring modulator, Ge photodetector, temperature sensor, on-chip heater, and temperature controller, all monolithically integrated on a 0.25 µm photonic BiCMOS technology platform. The integrated transmitter successfully provides stable and optimal 25 Gb/s modulation characteristics against external temperature fluctuation. © 2021 Chinese Laser Press

https://doi.org/10.1364/PRJ.413407

#### 1. INTRODUCTION

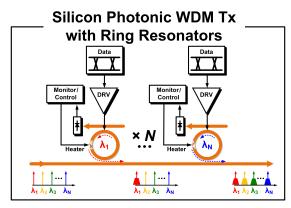

Si photonic transmitters based on ring resonators are very attractive since they have small footprint, energy-efficient operation, and large modulation bandwidth. With these, they are expected to replace Si Mach–Zehnder modulators that are presently widely used in the data center interconnect applications [1–3]. In addition, Si ring modulators (RMs) with their wavelength-dependent characteristics can provide a very large data throughput capability with wavelength division multiplexing (WDM), as schematically shown in Fig. 1. Consequently, they attract a great amount of research interest for next-generation optical interconnect solutions that are needed for high-performance computing systems [4]. Furthermore, ring-resonator-based photonic switches are expected to play an important role for next-generation photonic switching systems [5].

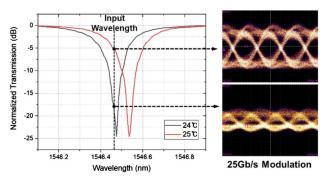

Ring resonator characteristics, however, are highly sensitive to temperature. For example, just a one degree temperature change can significantly degrade the modulation eye quality, as shown in Fig. 2, where measured transmission characteristics and 25 Gb/s eye diagrams are shown for a sample Si RM at two different temperatures with a fixed input wavelength. Consequently, a technique to maintain the correct temperature for optimal device performance is a necessity for any application of ring-resonator-based devices, including Si RMs. There are several previously reported temperature control (TC) techniques for ring resonator filters [6–9], switches [10,11], and modulators [12–17]. For resonator-based filters and switches,

the controller monitors the amount of transmission at the resonance wavelength where the transmitted optical power is either minimum or maximum, making the controller implementation relatively straightforward. However, because the RM input wavelength providing the maximum optical modulation amplitude (OMA) is away from the resonance wavelength [18], realizing a temperature control technique that determines and maintains the optimal temperature for the RM can be challenging. In Refs. [12–14], the average modulated optical power is monitored and locked to a set value with a closed-loop feedback. However, this set value must be externally supplied. In Ref. [15], the RM OMA is directly monitored by high-speed sampling of the designated modulation pattern with slope quantization. But high-speed sampling consumes a large amount of power, especially when the data rate is high. OMA maximization based on bit statistics using the training data sequence can achieve low-power operation [16], but maintaining the optimal condition when the temperature changes from the initial calibration condition may require additional calibration steps.

To alleviate the problems discussed above, we have previously reported a custom-designed temperature control IC with which the optimal temperature for the RM OMA is automatically determined in the calibration mode and is stably maintained in the lock mode with a 1-bit dithering technique [17]. This approach, however, requires continuous OMA monitoring in the lock mode, resulting in increased power consumption. In this paper, we present what we believe, to the

<sup>&</sup>lt;sup>2</sup>Current address: Samsung Electronics, Hwasung, 18448 Gyeonggi-do, Republic of Korea

<sup>&</sup>lt;sup>3</sup>IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

<sup>&</sup>lt;sup>4</sup>Technische Universität Berlin, Einsteinufer 25, 10587 Berlin, Germany

<sup>\*</sup>Corresponding author: wchoi@yonsei.ac.kr

**Fig. 1.** Block diagram of the silicon photonic WDM transmitter with ring resonators.

**Fig. 2.** Measured transmission curves and 25 Gb/s eye diagrams for different temperatures.

best of our knowledge, is a new approach in which the OMA monitoring block is used only in the calibration mode. This is achieved using an on-chip temperature sensor [19]. With this, the controller can determine and remember the optimal RM temperature in the calibration mode, and maintain this temperature in the lock mode. In this paper, we explain how our temperature control technique works and provide measurement results based on a 25 Gb/s Si photonic transmitter IC realized on the photonic BiCMOS technology platform [20], which contains monolithically integrated photonic and electronic components.

This paper is organized in four sections. In Section 2, we describe the details of our monolithically integrated Si photonic transmitter along with explanations for the temperature control algorithm. In Section 3, the measurement results for our transmitter are given. Finally, Section 4 concludes the paper. The initial results of this work were reported in Ref. [21], but in this paper, we provide significantly more detailed explanations for our transmitter and the temperature control algorithm is given. Furthermore, the experimental results that verify the stable operation of our transmitter against the larger temperature stress range (from 5°C to 15°C) are presented.

#### 2. RM TRANSMITTER WITH TC CIRCUIT

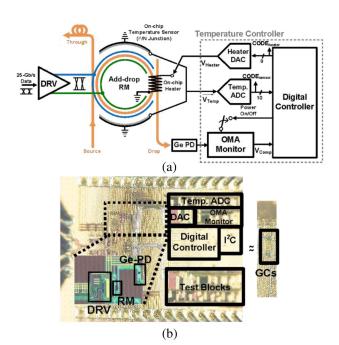

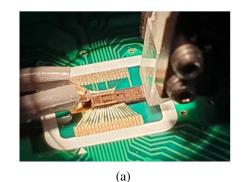

Figure 3(a) shows the block diagram of our custom-designed Si photonic transmitter IC and Fig. 3(b) is a photo of the

**Fig. 3.** (a) Block diagram and (b) fabricated chip photo of the monolithic silicon photonic transmitter with a temperature controller.

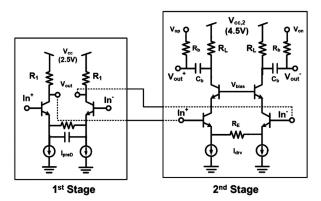

fabricated chip. It consists of an electronic driver, RM, Ge monitoring PD, on-chip heater, on-chip temperature sensor, and temperature controller. The driver amplifies externally supplied 25 Gb/s  $0.6V_{pp,diff}$  NRZ data and delivers  $3V_{pp,diff}$  to the Si depletion-type RM. The driver consists of two-stage amplifiers, as shown in Fig. 4. The first stage is designed so that it can buffer input electrical signals before they are delivered to the second stage, which has large-size transistors. It employs the RC degeneration technique that provides bandwidth enhancement by reducing gain in the low-frequency range [22]. The second stage uses the differential cascode structure so that it can generate  $3\,V_{\rm pp,diff}$  swing without any transistor breakdown. The output signals of the second stage are delivered to the RM with capacitive coupling so that desired RM bias voltages can be supplied. To design these amplifiers, electronic-photonic co-simulation with the newly developed large-signal SPICE model for the RM [23,24] is used so that the driver load resistance  $(R_L)$  in the second stage can be optimized for both

Fig. 4. Schematic of the RM driver circuits.

power consumption and the RM output optical eye performance. The power consumption of such a driver IC is 329 mW.

The RM has 12  $\mu$ m radius and is made up of 500 nm wide waveguides implemented on the standard Si photonic SOI structure. An optical drop port is added to the RM so that OMA can be directly monitored with an integrated Ge PD, as shown in Fig. 3(a). An N-doped Si heater is placed within the ring waveguide, which can change the RM temperature up to 40% of its 8.293 nm free spectral range (FSR). PN-junction-based temperature sensors are placed above and below the RM, which provide voltage signals representing the RM temperature.

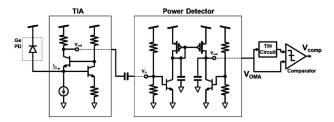

The temperature controller has four building blocks: an OMA monitor, an ADC for temperature sensor output, a DAC for on-heat heater driving, and a digital controller, as shown in Fig. 3(a). The OMA monitor contains a transimpedance amplifier (TIA) with a 40 dB $\Omega$  gain and a 20 GHz bandwidth, plus a power detector, track-and-hold (T/H) circuit, and a comparator, as shown in Fig. 5 [17]. Modulated optical signals from the drop port of the RM are converted into electrical signals and amplified with the monitor Ge PD and the TIA, and the power detector produces  $V_{\rm OMA}$  representing RM OMA. With the T/H and the comparator,  $V_{\rm comp}$  is produced, which represents the latest and largest value of  $V_{\rm OMA}$  so that  $V_{\rm OMA}$  is continuously updated during the calibration mode.

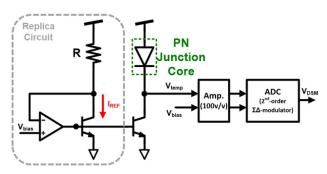

Figure 6 shows the temperature sensor ADC, which converts the voltage signals across the PN junctions near the RM at a fixed current into a 10-bit digital code. This block is composed of a reference replica circuit, an amplifier, and a second-order  $\Sigma - \Delta$  modulator ADC [25]. The temperature sensor has 0.2°C/LSB sensitivity with a maximum range of 50°C. With the reference current ( $I_{\rm REF}$ ) determined in the

**Fig. 5.** Schematic of the OMA monitor block.

**Fig. 6.** Schematic of the temperature sensor ADC.

replica circuit,  $V_{\rm temp}$  represents the voltage across the PN junction at a given RM temperature corresponding to  $I_{\rm REF}$ . The voltage difference between the  $V_{\rm bias}$  and  $V_{\rm temp}$  is amplified and converted to a 10-bit digital code (CODE<sub>sensor</sub>).

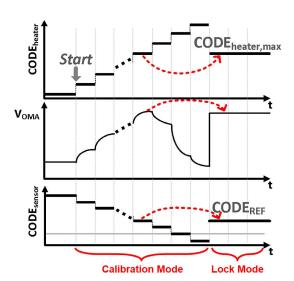

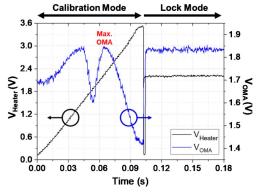

Figure 7 shows the timing diagram for the temperature control operation, which is divided into two modes: the calibration mode and the lock mode. In the calibration mode, the controller provides increasing voltages ( $V_{\rm Heater}$ ) to the on-chip heater through the heater DAC output digital codes (CODE<sub>heater</sub>) so that the RM temperature can be scanned in the pre-determined range. With this, the RM OMA ( $V_{\rm OMA}$ ) changes as the RM modulation characteristics change with changing temperature. Simultaneously, the RM temperature is monitored with the temperature ADC output code (CODE<sub>sensor</sub>). After the scan is complete, the digital controller determines the maximum OMA and the temperature at which the maximum OMA is achieved and stores them as CODE<sub>heater, max</sub> and CODE<sub>REF</sub>. This approach can reduce the power consumption a lot since the OMA block is turned off at the lock mode; however, it cannot track the laser wavelength due to its aging or environment. If such a change occurs, a higher-level control is required in which the RM is recalibrated.

In the lock mode, the heater voltage is set to the value determined to produce the maximum OMA in the calibration mode. Then, to maintain the maximum OMA against any temperature perturbation, a PID control is applied to the heater voltage so that the optimum RM temperature is maintained. The OMA monitor block is turned off in the lock mode so that power can be saved. The on-chip digital controller is implemented by synthesis based on a 0.25  $\mu m$  CMOS standard library provided by the IHP Photonic BiCMOS technology and is composed of more than 2000 transistors.

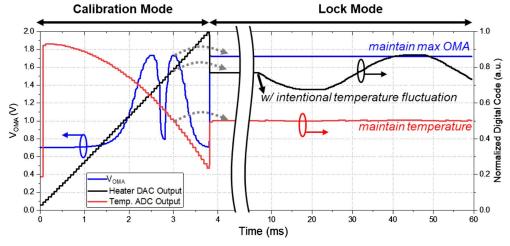

Figure 8 shows the simulated results for the temperature control operation. For this simulation, the temperature-dependent characteristics of the RM, the on-chip heater, and the on-chip temperature sensor are first measured, and their behavior models are implemented with Verilog-A, a hardware description language. Then, Verilog-A simulation is performed that can account for behaviors of the entire analog and

**Fig. 7.** Timing diagram for the temperature control operation.

Fig. 8. Simulation results for the temperature control operation with Verilog-A behavior models.

digital circuits as well as the RM, the on-chip heater, and the temperature sensor. As shown in Fig. 8, with the sweeping heater DAC code, the RM OMA and the temperature ADC code change widely. Two temperature conditions are found for the maximum RM OMA since the RM transmission characteristic is symmetric around the resonance wavelength, as can be seen in Fig. 2. The digital controller is programmed to take the latter one. As shown in the figure, the controller correctly determines the RM temperature and the heater voltage that produce the maximum OMA in the calibration mode, and maintains the maximum OMA and the corresponding RM temperature by modifying the heater voltage when the RM temperature fluctuation is intentionally introduced in the lock mode.

#### 3. MEASUREMENT RESULTS

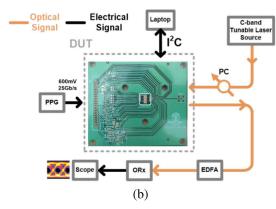

Figure 9(a) shows a photo for the chip under probing, and Fig. 9(b) shows the block diagram for the measurement setup. The chip is mounted on an FR4 PCB, and supply and bias voltages are provided through bonding wires. NRZ data  $(0.6V_{\rm pp,diff}, 25 \text{ Gb/s PRBS } \bar{2}^{31}-1)$  are delivered to the chip with direct RF probing. Grating couplers are used for photonic I/O. The RM output optical signals are amplified with an EDFA, and an optical receiver along with an electric oscilloscope is used for the eye measurement. The RM has a near 6 dB loss at the operation point. The transmitter IC contains an I<sup>2</sup>C bus, which externally controls the IC as well as monitors internal signals such as the DAC and ADC codes during the measurement. In the calibration mode, the temperature sensor consumes 2.6 mW, and the OMA monitor block consumes 6.325 mW. On the other hand, high-speed TIA consumes most of the power: 5.075 mW. The digital controller consumes only 725 µW. Since the OMA monitor block is only used for the calibration mode and most of the operation will be in the lock mode, the total power consumption for the temperature control is 3.325 mW, excluding the heater

Figure 10 shows the measured RM transmission characteristics with different amounts of on-chip heater powers. With

**Fig. 9.** (a) Photo and (b) block diagram of the measurement setup.

the increasing heater power, the resonance wavelength shifts to the larger wavelength. With the maximum heater power of 20.7 mW, which is limited by the allowed maximum supply voltage to the heater DAC in the photonic BiCMOS technology, the resonant wavelength shift of 3.27 nm is possible, which corresponds to a temperature change of 45° or 40% of the RM FSR at room temperature. Therefore, the TC IC cannot maintain the optimal RM temperature if the resonant wavelength is not within such range. However, the on-chip heater efficiency and the temperature tuning range can be greatly improved with

**Fig. 10.** Measured transmission curve of the RM with different on-chip heater powers.

better heater fabrication technology [26] and/or the thermal isolation technique [27,28].

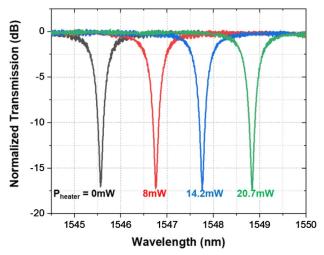

Figure 11 shows the measurement results for the temperature sensing block. Figure 11(a) shows current-voltage (I-V)

**Fig. 11.** (a) Measured *I-V* curve for the temperature sensor and (b) measured ADC output code with different temperatures.

characteristics of the PN junction sensors at different temperatures. As shown in Fig. 6, the voltage at the PN junction is determined to generate the reference current ( $I_{\rm REF}$ ), which is set to 20  $\mu$ A for our measurement. For this measurement, the stage temperature on which our transmitter IC is placed is changed. Figure 11(b) shows the resulting ADC codes delivered to the digital controller.

Figure 12 shows the measurement results for heater voltage ( $V_{\rm Heater}$ ) and RM OMA ( $V_{\rm OMA}$ ) in the calibration and lock modes. The heater voltage is scanned with 13 mV resolution for a 1-bit digital code, resulting in a significant amount of the RM OMA changes. It can be clearly observed that the digital controller correctly determines the heater voltage for the maximum RM OMA and maintains it in the lock mode.

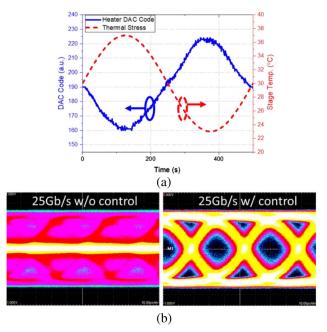

Figure 13(a) shows the measurement results in the lock mode when the RM goes through a sinusoidal thermal stress

Fig. 12. Measurement results for heater voltage ( $V_{\rm Heater}$ ) and RM OMA ( $V_{\rm OMA}$ ) in calibration and lock modes.

**Fig. 13.** Measurement results in the lock mode with thermal stress showing (a) heater voltage ( $V_{\rm Heater}$ ) and (b) 25 Gb/s eye diagrams.

|                                         | 15′ JSCC<br>[12]                   | 18' ISSCC<br>[13]                             | 20' ISSCC<br>[14]                            | 16′ JSSC<br>[15]                        | 16' JSSC<br>[16]    | 19′ JLT<br>[17]                                                     | This Work                                                         |

|-----------------------------------------|------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------|---------------------|---------------------------------------------------------------------|-------------------------------------------------------------------|

| Process                                 | 130 nm SOI<br>SiPh + 65 nm<br>CMOS | 100 nm SOI<br>SiPh + 65 nm<br>CMOS            | SiPh + 28 nm<br>CMOS                         | 130 nm SOI<br>SiPh + 40 nm<br>CMOS      | 45 nm<br>CMOS SOI   | 0.25 μm<br>BiCMOS                                                   | 0.25 μm<br>Photonic<br>BiCMOS                                     |

| Wavelength                              | 1550 nm                            | 1310 nm                                       | 1310 nm                                      | 1550 nm                                 | 1180 nm             | 1550 nm                                                             | 1550 nm                                                           |

| Data Rate                               | 25 Gb/s                            | 10 Gb/s                                       | 112 Gb/s                                     | 2 Gb/s                                  | 5 Gb/s              | 25 Gb/s                                                             | 25 Gb/s                                                           |

| Driver<br>Integration                   | Yes (Wire-<br>bonded)              | Yes (3D face-<br>to-face)                     | Yes (3D face-<br>to-face)                    | Yes (Wire-<br>bonded)                   | Yes<br>(Monolithic) | No                                                                  | Yes<br>(Monolithic)                                               |

| Controller<br>Integration               | No (Off-chip<br>PD)                | Yes (3D face-<br>to-face)                     | Yes (3D face-<br>to-face)                    | No (Off-chip<br>DAC)                    | Yes<br>(Monolithic) | No<br>(Off-chip PD)                                                 | Yes<br>(Monolithic)                                               |

| Scheme                                  | Average power                      | Analog closed-<br>loop w/digital<br>reconfig. | Normalized<br>average power<br>stabilization | OMA monitor<br>w/slope-<br>quantization | Bit-statistics      | OMA monitor<br>with power<br>detector &<br>without step<br>approach | OMA<br>monitor<br>with<br>temperature<br>sensing &<br>PID control |

| Manual Reference<br>Setting             | Yes                                | Yes                                           | Yes                                          | No                                      | No                  | No                                                                  | No                                                                |

| Resonance<br>Wavelength<br>Tuning Range | N/A                                | N/A                                           | Not reported<br>(50 mW power<br>dissipation) | 5 nm                                    | 2.5 nm              | 0.55 nm                                                             | 3.27 nm                                                           |

Not reported

2.9 mW

Table 1. Performance Comparison for Silicon Photonic Transmitters with Ring Modulators and Temperature Controllers

"Excluding heater power

Temp. Controller

Power<sup>a</sup>

of 15°C with a 500 s period. For the thermal stress, the stage temperature is intentionally changed where the PCB containing the transmitter IC is, as shown by the red dotted line in the figure. The blue line shows the internal heater DAC code representing voltages applied to the on-chip heater. As the stage temperature changes, the digital controller changes the heater voltage so that the RM remains at the same temperature as the temperature determined to provide the maximal OMA in the calibration mode. Figure 13(b) shows the accumulated eye diagrams during this thermal stress for 8 min with and without temperature control. The eye remains open with 5.2 dB extinction ratio even if the stage temperature changes up to 15°C; however, the eye completely closes without control.

0.17 mW

0.15 mW

Table 1 compares the performance of our transmitter IC with recently reported RM temperature control ICs. As can be seen in the table, only in Ref. [16] and the present work, the temperature controller can determine the RM optimal temperature without any external reference and monolithic integration is achieved. The power consumption reported in Ref. [16] is much smaller than our result, which is due to the much advanced SOI CMOS technology used in Ref. [16], not the temperature control algorithm employed. It should also be noted that our temperature control scheme does not depend on the data rate as schemes like in Ref. [15].

#### 4. CONCLUSION

We present a fully integrated Si photonic transmitter containing a high-speed RM with an on-chip heater and a temperature

sensor, a monitor Ge PD, and analog and digital temperature controllers. With two-step calibration and lock mode operations, our transmitter can automatically determine the temperature at which the RM has the maximum OMA and maintain this condition against any temperature fluctuation. Our temperature control scheme is energy efficient and does not depend on the details of RM data rates. With complete monolithic integration of photonic and electronic components achieved with the photonic BiCMOS technology, our transmitter can provide the reduced transmitter size as well as the smaller I/O pin numbers. We also believe that our approach based on photonic and electronic integration can be applied to other photonic devices that require temperature control for best performance.

3.91 mW

3.325 mW

0.72 mW

**Funding.** Ministry of Trade, Industry and Energy (10065666); National Research Foundation of Korea (2020R1A2C201508911); Yonsei University.

**Acknowledgment.** The authors thank the IC Design Education Center (IDEC) for EDA tool support.

**Disclosures.** The authors declare no conflicts of interest.

### **REFERENCES**

W. Bogaerts, P. de Heyn, T. van Vaerenbergh, K. de Vos, S. Kumar Selvaraja, T. Claes, P. Dumon, P. Bienstman, D. van Thourhout, and R. Baets, "Silicon microring resonators," Laser Photon. Rev. 6, 47–73 (2012).

- G. Li, A. V. Krishnamoorthy, I. Shubin, J. Yao, Y. Luo, H. Thacker, X. Zheng, K. Raj, and J. E. Cunningham, "Ring resonator modulators in silicon for interchip photonic links," IEEE J. Sel. Top. Quantum Electron. 19, 95–113 (2013).

- H. Li, B. Casper, G. Balamurugan, M. Sakib, J. Sun, J. Driscoll, R. Kumar, H. Jayatilleka, H. Rong, and J. Jaussi, "A 112 Gb/s PAM4 silicon photonics transmitter with microring modulator and CMOS driver," J. Lightwave Technol. 38, 131–138 (2020).

- C. Sun, M. T. Wade, Y. Lee, J. S. Orcutt, L. Alloatti, M. S. Georgas, A. S. Waterman, J. M. Shainline, R. R. Avizienis, S. Lin, B. R. Moss, R. Kumar, F. Pavanello, A. H. Atabaki, H. M. Cook, A. J. Ou, J. C. Leu, Y.-H. Chen, K. Asanović, R. J. Ram, M. A. Popović, and V. M. Stojanović, "Single-chip microprocessor that communicates directly using light," Nature 528, 534–538 (2015).

- Y. Shen, X. Meng, Q. Cheng, S. Rumley, N. Abrams, A. Gazman, E. Manzhosov, M. S. Glick, and K. Bergman, "Silicon photonics for extreme scale systems," J. Lightwave Technol. 37, 245–259 (2019).

- K. Padmaraju, D. F. Logan, T. Shiraishi, J. J. Ackert, A. P. Knights, and K. Bergman, "Wavelength locking and thermally stabilizing microring resonators using dithering signals," J. Lightwave Technol. 32, 505–512 (2014).

- H. Jayatilleka, K. Murray, M. Á. Guillén-Torres, M. Caverley, R. Hu, N. A. F. Jaeger, L. Chrostowski, and S. Shekhar, "Wavelength tuning and stabilization of microring-based filters using silicon in-resonator photoconductive heaters," Opt. Express 23, 25084–25097 (2015).

- J. C. C. Mak, W. D. Sacher, T. Xue, J. C. Mikkelsen, Z. Yong, and J. K. S. Poon, "Automatic resonance alignment of high-order microring filters," IEEE J. Quantum Electron. 51, 0600411 (2015).

- K. Yu, C. Li, H. Li, A. Titriku, A. Shafik, B. Wang, Z. Wang, R. Bai, C.-H. Chen, M. Fiorentino, P. Y. Chiang, and S. Palermo, "A 25 Gb/s hybrid-integrated silicon photonic source-synchronous receiver with microring wavelength stabilization," IEEE J. Solid-State Circuits 51, 2129–2141 (2016).

- R. Enne, M. Hofbauer, N. Zecevic, B. Goll, and H. Zimmermann, "Integrated analogue-digital control circuit for photonic switch matrices," Electron. Lett. 52, 1045–1047 (2016).

- Z. Zhu, A. Gazman, D. Gidony, Y. Shen, K. Shepard, and K. Bergman, "Single-wire DAC/ADC control and feedback of silicon photonic ring resonator circuits for wavelength switching," in *Optical Fiber Communication Conference* (OSA, 2018), paper W2A.32.

- H. Li, Z. Xuan, A. Titriku, C. Li, K. Yu, B. Wang, A. Shafik, N. Qi, Y. Liu, R. Ding, T. Baehr-Jones, M. Fiorentino, M. Hochberg, S. Palermo, and P. Y. Chiang, "A 25 Gb/s, 4.4 V-swing, AC-coupled ring modulatorbased WDM transmitter with wavelength stabilization in 65 nm CMOS," IEEE J. Solid-State Circuits 50, 3145–3159 (2015).

- 13. Y. Thonnart, M. Zid, J. L. Gonzalez-Jimenez, G. Waltener, R. Polster, O. Dubray, F. Lepin, S. Bernabe, S. Menezo, G. Pares, O. Castany, L. Boutafa, P. Grosse, B. Charbonnier, and C. Baudot, "A 10 Gb/s Siphotonic transceiver with 150 µW 120 µs-lock-time digitally supervised analog microring wavelength stabilization for 1 Tb/(s·mm) 2 die-to-die optical networks," in *IEEE International Solid-State Circuits Conference* (IEEE, 2018), pp. 350–352.

- H. Li, G. Balamurugan, M. Sakib, R. Kumar, H. Jayatilleka, H. Rong, J. Jaussi, and B. Casper, "12.1 A 3D-integrated microring-based

- 112 Gb/s PAM-4 silicon-photonic transmitter with integrated nonlinear equalization and thermal control," in *IEEE International Solid-State Circuits Conference* (IEEE, 2020), pp. 208–210.

- S. Agarwal, M. Ingels, M. Pantouvaki, M. Steyaert, P. Absil, and J. Van Campenhout, "Wavelength locking of a Si ring modulator using an integrated drop-port OMA monitoring circuit," IEEE J. Solid-State Circuits 51, 2328–2344 (2016).

- C. Sun, M. Wade, M. Georgas, S. Lin, L. Alloatti, B. Moss, R. Kumar, A. H. Atabaki, F. Pavanello, J. M. Shainline, J. S. Orcutt, R. J. Ram, M. Popovic, and V. Stojanovic, "A 45 nm CMOS-SOI monolithic photonics platform with bit-statistics-based resonant microring thermal tuning," IEEE J. Solid-State Circuits 51, 893–907 (2016).

- M.-H. Kim, L. Zimmermann, and W.-Y. Choi, "A temperature controller IC for maximizing Si micro-ring modulator optical modulation amplitude," J. Lightwave Technol. 37, 1200–1206 (2019).

- H. Yu, D. Ying, M. Pantouvaki, J. Van Campenhout, P. Absil, Y. Hao, J. Yang, and X. Jiang, "Trade-off between optical modulation amplitude and modulation bandwidth of silicon micro-ring modulators," Opt. Express 22, 15178–15189 (2014).

- S. Saeedi and A. Emami, "Silicon-photonic PTAT temperature sensor for micro-ring resonator thermal stabilization," Opt. Express 23, 21875–21883 (2015).

- D. Knoll, S. Lischke, A. Awny, and L. Zimmermann, "(Invited) SiGe BiCMOS for Optoelectronics," ECS Trans. 75, 121–139 (2016).

- M. Kim, M.-H. Kim, Y. Jo, H.-K. Kim, S. Lischke, C. Mai, L. Zimmermann, and W.-Y. Choi, "A fully integrated 25 Gb/s Si ring modulator transmitter with a temperature controller," in *Optical Fiber Communication Conference* (OSA, 2020), paper T3H.7.

- 22. B. Razavi, Design of Integrated Circuits for Optical Communications (Wiley, 2012).

- M. Kim, K. Park, W.-S. Oh, C. Mai, S. Lischke, L. Zimmermann, and W.-Y. Choi, "A 4 × 25-Gbps monolithically integrated Si photonic WDM transmitter with ring modulators," in *IEEE Optical Interconnects Conference (OI)* (IEEE, 2019), pp. 1–2.

- M. Kim, M. Shin, M.-H. Kim, B.-M. Yu, Y. Kim, Y. Ban, S. Lischke, C. Mai, L. Zimmermann, and W.-Y. Choi, "Large-signal SPICE model for depletion-type silicon ring modulators," Photon. Res. 7, 948–954 (2019).

- M. A. P. Pertijs, K. A. A. Makinwa, and J. H. Huijsing, "A CMOS smart temperature sensor with a 3σ inaccuracy of 0.1°C from 55°C to 125°C," IEEE J. Solid-State Circuits 40, 2805–2815 (2005).

- M. Pantouvaki, S. A. Srinivasan, Y. Ban, P. De Heyn, P. Verheyen, G. Lepage, H. Chen, J. De Coster, N. Golshani, S. Balakrishnan, P. Absil, and J. Van Campenhout, "Active components for 50 Gb/s NRZ-OOK optical interconnects in a silicon photonics platform," J. Lightwave Technol. 35, 631–638 (2017).

- P. Dong, W. Qian, H. Liang, R. Shafiiha, D. Feng, G. Li, J. E. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "Thermally tunable silicon racetrack resonators with ultralow tuning power," Opt. Express 18, 20298–20304 (2010).

- I. Shubin, X. Zheng, H. Thacker, S. S. Djordjevic, S. Lin, P. Amberg, J. Lexau, K. Raj, J. E. Cunningham, and A. V. Krishnamoorthy, "All solid-state multi-chip multi-channel WDM photonic module," in *IEEE 65th Electronic Components and Technology Conference (ECTC)* (IEEE, 2015), pp. 1293–1298.