# Back-Illuminated Double-Avalanche-Region Single-Photon Avalanche Diode

Eunsung Park, Doyoon Eom, Myeong-Hun Yu, Yun-Mi Moon, Dae-Hwan Ahn, Jongtae Ahn, Do Kyung Hwang, Woo-Young Choi, *Member, IEEE*, and Myung-Jae Lee, *Member, IEEE*

(Invited Paper)

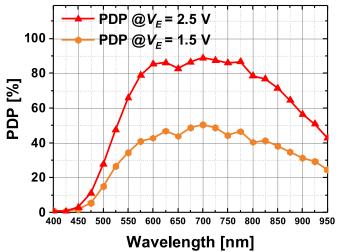

Abstract—The key features of a single-photon avalanche diode (SPAD) are its ability to detect a single photon and provide a digital signal output. The avalanche multiplication process, which generates a detectable electrical signal that can be amplified up to a high voltage without the need for additional circuits, allows SPADs to detect individual photons. Specifically, a SPAD fabricated in CMOS technology can detect near-infrared (NIR) signals, which is a crucial requirement in many applications such as light detection and ranging (LiDAR), time-of-flight (ToF) imaging, and NIR optical tomography. These applications require specific performance characteristics, for example, high photon detection probability (PDP). In this article, we propose an optimized SPAD developed based on 40 nm backside illuminated (BSI) CMOS image sensor (CIS) technology. The SPAD is designed and fabricated using a heavily doped p-type (P+) and a retrograde doped deep n-well (DNW) junction. The doping-optimized guard-ring (GR) for the expansion of the avalanche multiplication region maximizes PDP, while maintaining its original capability, premature edge breakdown (PEB) prevention at the edge of the junction. We demonstrate the effectiveness of GR optimization by comparing the electrical and optical experimental results with the conventional SPAD. The proposed double-avalanche-region (DAR) SPAD achieves a peak PDP of about 89% at the wavelength of 700 nm and a PDP of 45% at 940 nm, which are the highest values among SPADs reported so far at the excess bias voltage of 2.5 V. The dark count rate (DCR) is 27 cps/ $\mu$ m<sup>2</sup> and the full width at half-maximum (FWHM) of the timing jitter is 89 ps at the same operating condition.

Index Terms—Avalanche photodiode (APD), back-illuminated single-photon avalanche diode (SPAD), CMOS image sensor (CIS)

Manuscript received 1 April 2023; revised 28 June 2023 and 30 August 2023; accepted 18 September 2023. Date of publication 17 October 2023; date of current version 15 December 2023. This work was supported in part by the Korea Institute of Science and Technology Institution Program under Grant 2E32242, and in part by the National Research Foundation of Korea under Grant 2021M3D1A2046731. (Corresponding authors: Woo-Young Choi; Myung-Jae Lee.)

Eunsung Park and Doyoon Eom are with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea, and also with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea (e-mail: es.park@kist.re.kr; dja1995@kist.re.kr).

Myeong-Hun Yu, Yun-Mi Moon, Dae-Hwan Ahn, Jongtae Ahn, Do Kyung Hwang, and Myung-Jae Lee are with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul 02792, South Korea (e-mail: hot2029@kist.re.kr; yunmi@kist.re.kr; daehwan23@kist.re.kr; shea13@kist. re.kr; dkhwang@kist.re.kr; mj.lee@kist.re.kr).

Woo-Young Choi is with the Department of Electrical and Electronic Engineering, Yonsei University, Seoul 03722, South Korea (e-mail: wchoi@yonsei.ac.kr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSTQE.2023.3322354.

Digital Object Identifier 10.1109/JSTQE.2023.3322354

technology, detector, diode, electronic-photonic integration, geiger-mode avalanche photodiode (G-APD), high-volume manufacturing, integrated optoelectronics, integration of photonics in standard CMOS technology, light detection and ranging (LiDAR), near infrared (NIR), optical sensing, optical sensor, photodetector, photodiode, photomultiplier, RGB-D sensor, semiconductor device, sensor, silicon, wafer-scale.

# I. INTRODUCTION

SINGLE-PHOTON avalanche diode (SPAD) is an optoelectronic device capable of detecting a single photon and providing a digital output signal. The basic structure of a SPAD is based on a p-n junction diode, engineered to operate in Geiger mode by reverse-biasing above its breakdown voltage  $(V_B)$ . The abilities to detect a single photon and to generate a digital output make SPADs a key enabling technology in a wide range of applications, spanning from time-of-flight (ToF) imaging systems to quantum applications. Due to their operating principle and versatility across various applications, SPADs have been the subject of continuous study and development. Additionally, fabricating SPADs using CMOS technology offers several advantages, such as integration with electronics, scalability, cost-effectiveness, and high-density SPAD arrays. As a result, SPAD development has advanced in various CMOS processes since the work by E. Charbon [1]. The typical way of fabricating a CMOS SPAD is using frontside illumination (FSI) processes which has the advantages of a simple fabrication process and high yield [1], [2], [3], [4], [5], [6], [7], [8], [9]. However, the most critical limitation of the FSI approach is reduced sensitivity to light because the metal layers and electronic components on the front side can block or scatter the incoming photons. To overcome this limitation, SPADs have been developed using backside illumination (BSI) processes [10], [11], [12], [13], [14], [15], [16], [17]. The BSI technology enhances the sensitivity of SPADs because there are no components blocking the incoming photons. In addition, the thickness of the remaining Si wafer after the backside thinning can be adjusted to optimize the SPAD performance for each target wavelength range. Recently, the most desirable applications based on CMOS SPADs are light detection and ranging (LiDAR) for smartphones and autonomous vehicle systems at near-infrared (NIR) wavelengths, and SPADs based on the BSI technology have deeper avalanche multiplication regions and thicker absorption regions, providing the advantage of higher

© 2023 The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

chance of detecting carriers generated by NIR photons. One of the most important factors in evaluating the performance of a SPAD is the photon detection probability (PDP), which represents the probability that an incident photon triggers an avalanche multiplication. There are various advantages to the systems when improving PDP in SPAD-based sensors. First, in a ToF system [18], [19], [20], a high PDP can enable the detection of a weaker return signal, which may allow for the use of a lower-power laser source, leading to reduced power consumption. Also, the system can more effectively distinguish true signals from the background noise, leading to the improved signal-to-noise ratio (SNR). And higher PDP means that the detector is more likely to detect weak return signals accurately, allowing better detection of distant or low-reflectivity objects in LiDAR applications. There are several ways to improve the PDP of the SPAD fabricated in BSI technology by using specialized process options such as microlens and backside trench guide. However, these processes can increase process complexity and, consequently, result in increased fabrication cost.

In this article, in order to improve the PDP performance, we propose a double-avalanche-region (DAR) SPAD which has an expanded avalanche multiplication region with doping optimization. The DAR SPAD is fabricated in 40 nm CMOS image sensor (CIS) technology which is the most advanced technology for CMOS SPADs reported to date. The full performance of the DAR SPAD is clearly characterized and analyzed, and the electrical and optical characteristics of the conventional SPAD and the DAR SPAD are compared to prove the effectiveness of the optimization. Through the optimization, the DAR SPAD achieves an excellent PDP of 45% at the wavelength of 940 nm along with a small timing jitter of 89 ps at the full width at half maximum (FWHM).

The structure of this article is outlined as follows. Section II proposes the DAR SPAD structure and explains how the proposed SPAD is optimized. In Section III, measurement results such as the current-voltage (I-V) characteristics, dark count rate (DCR), temperature dependency, PDP, and timing jitter are presented. A comparative evaluation with other state-of-the-art SPADs is offered in Section IV. Finally, the article is concluded in Section V.

### II. DEVICE STRUCTURE AND SIMULATION RESULTS

In a SPAD, there are two mechanisms that can affect triggering the avalanche multiplication of the charge carrier in response to an electric field [21]. First, drift is the movement of the charge carriers caused by an electric field. When a reverse bias is applied to a SPAD through the p-n junction, it exerts a force on the charge carriers, causing them to quickly move to the avalanche multiplication region. Secondly, diffusion is the process by which charge carriers move from an area of higher concentration to an area of lower concentration. Diffusion is less related to the electric field compared to the drift, but the electric field can affect the behavior of diffusion indirectly by altering the concentration gradient of the carriers, which in turn affects the rate of diffusion [22], [23], [24]. In a SPAD, both drift and diffusion can affect PDP, and the importance of each mechanism depends on the

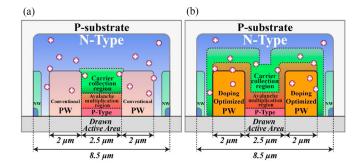

Fig. 1. Illustrated images: (a) conventional SPAD without GR doping optimization and (b) DAR SPAD with GR doping optimization.

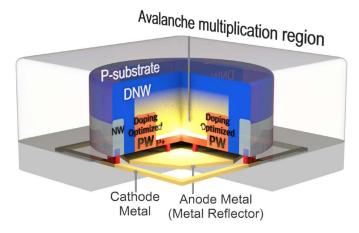

Fig. 2. Cross-section of the DAR SPAD.

device design and operating conditions. To improve the PDP of the SPAD in the BSI process, several techniques were introduced as mentioned in Section I, such as microlens and backside trench guide. However, implementing an additional structure requires specialized equipment and processes, which are more difficult to control and result in higher manufacturing costs. The most costeffective and simple way is optimizing the doping concentration without any addition to expand the avalanche multiplication region and carrier collection region that can directly affect PDP as shown in Fig. 1. Even if the drawn active areas are the same as the P-Type region in Fig. 1(a), (b), it is possible to extend the avalanche multiplication over the guard-ring (GR) region by optimizing the doping concentration as illustrated in Fig. 1(b). This also results in an extension of the carrier collection region, and therefore it becomes more effective at capturing the carriers generated by incident photons, leading to an increase in PDP.

In order to check and demonstrate the proposed technique, as shown in Fig. 2, the DAR SPAD is fabricated in 40 nm BSI CIS technology based on a circular shape. The SPAD is composed of a heavily doped p-type region, P+, and retrograde doped n-type region, deep n-well (DNW), that are joined together to form a p-n junction. To prevent edge breakdown and improve PDP, the doping-optimized p-well (PW) GR is placed around the p-n junction of the SPAD. The drawn active area of the SPAD consists of the p-n junction, with a diameter of 2.5  $\mu$ m, and the GR has been included with a width of 2  $\mu$ m. Additionally,

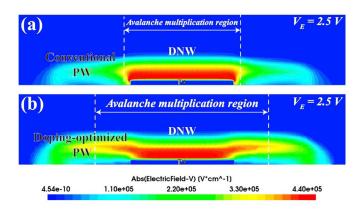

Fig. 3. E-field profile at  $V_E=2.5~\rm{V}$ : (a) SPAD with conventional PW GR and (b) SPAD with doping-optimized PW GR.

to prevent breakdown and/or leakage current between GR and cathode, 0.5  $\mu m$  space has been included. The device has a diameter of 8.5  $\mu m$ , with a 0.5  $\mu m$  cathode. The p-epi thickness is around 4  $\mu m$  after the backside etching process, and it has been equipped with a metal reflector and an anti-reflection coating (ARC). The only difference between the conventional SPAD and DAR SPAD is the doping profile of their PW GRs.

The TCAD simulation was conducted to check E-field profiles of the SPADs at the excess bias voltage ( $V_E$ ) of 2.5 V and the results are depicted in Fig. 3(a) and (b), showing their avalanche multiplication regions, respectively. The conventional SPAD has a lower doping concentration, which effectively prevents premature edge breakdown (PEB) at the edge of the junction but limits its ability to collect carriers generated by incident photons as shown in Fig. 3(a). On the other hand, the DAR SPAD has a higher doping concentration in the GR, which extends both the avalanche multiplication region and carrier collection region which allows for better carrier collection, resulting in a higher PDP while still preventing the PEB as shown in Fig. 3(b). In Section III, the characteristics of the two SPADs are clearly evaluated through electrical and optical experiments so that it demonstrates the effectiveness of the GR optimization.

# III. EXPERIMENTAL RESULTS

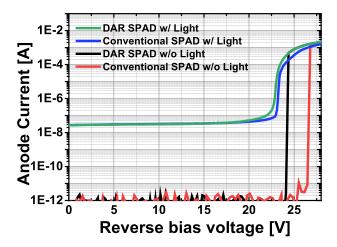

I-V characteristics can be used to observe the operation of a device that functions as a SPAD. The key operating method of a SPAD is the repetition of avalanche breakdown, which occurs when a high electric field is applied across the device, causing carriers to gain energy and collide with other atoms in the silicon through impact ionization. These newly released free carriers, in turn, collide with other atoms even more free carriers, and so on, leading to an avalanche effect that can cause the device to breakdown. The resulting avalanche breakdown can be observed through the I-V graph, as shown in Fig. 4. The performance of the two proposed SPADs is evaluated under both dark and ambient light conditions at room temperature. Specifically, the conventional SPAD with low GR doping concentration exhibits a  $V_B$  of 23.6 V, while the DAR SPAD with high GR doping concentration shows a slightly lower  $V_B$  of 23.3 V.

Fig. 4. Results of I-V characteristics of the two SPADs.

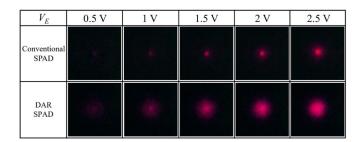

Fig. 5. Results of light-emission tests of the two SPADs at the various  $V_E$ .

The active area of a SPAD refers to the region of the p-n junction that is sensitive to incident photons and capable of generating an avalanche breakdown when a photon is detected. To calculate the PDP of a SPAD by using the formula depicted (1), the SPAD active area is a critical parameter that needs to be determined.

PDP [%] =

$$\frac{\# of \ counts - DCR}{\{P_{opt}/\frac{hc}{\lambda}\} \times \frac{SPAD \ active \ area}{ref. \ PD \ area}} \times 100$$

(1)

Typically, the *SPAD active area* is defined by the layout of the device, and the drawn active area illustrated in Fig. 1 is used for PDP calculations. However, the optimization of the doping concentration in the GR can lead to an extension of the avalanche multiplication region beyond the drawn p-n junction. When this happens, the PDP calculation based on the drawn active area may not be accurate. To define the effective active area that can be considered as the multiplication region, two measurements were conducted.

The light emission test (LET) is one of the experiments that can define the effective active area of a SPAD as the avalanche multiplication can lead to the emission of photons [25], [26], [27]. These photons can be detected using a microscope and image sensor and can help estimate the effective active area of a SPAD. The results of the LETs, as shown in Fig. 5, indicate the emission of light due to avalanche multiplication at various voltage levels, from  $V_E = 0.5$  V to  $V_E = 2.5$  V in 0.5 V steps. Basically, the two SPADs do not suffer from PEB and the results provide insight into the effective active areas of the SPADs. As

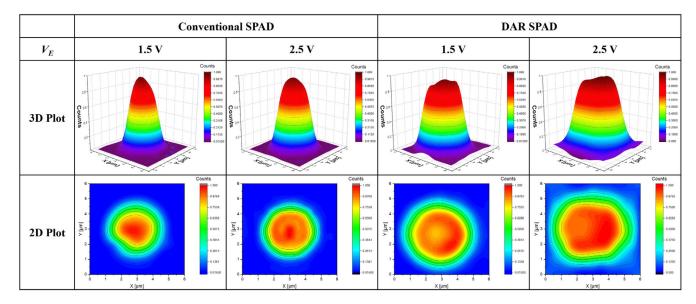

Fig. 6. Results of laser-scanning microscopy at the various excess bias voltages.

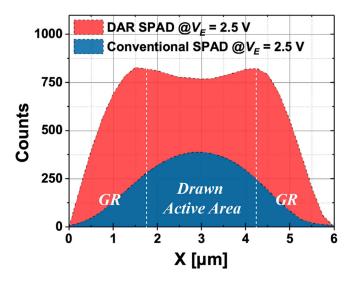

the applied  $V_E$  increases to both conventional and DAR SPADs, the electric field becomes wider and stronger, which can be demonstrated by observing the expansion of the multiplication region through changes in both light intensity and area. Although the two SPADs have the same drawn active area, they exhibit different levels of expansion in response to increases in  $V_E$ . While all experimental conditions were the same, there was no significant difference in light intensity when comparing the LET results of the conventional SPAD and the DAR SPAD. However, it was observed that the lighting area, which presents the avalanche multiplication region, was significantly larger in the DAR SPAD. To investigate the accurate effective active areas of the two SPADs further, an experimental study using laser scanning microscopy (LSM) is conducted. The LSM experiment is used to detect the exact avalanche multiplication regions of the SPADs by measuring the number of photon pulses from the SPAD when a laser beam is scanned across the SPAD and

Fig. 8. PDP results of DAR SPAD.

reconstructing an image from the collected data. Specifically, a 637 nm continuous laser was used for the light source, and an oscilloscope was used as a detector to measure the number of photon pulses from the SPADs operating with a 200  $k\Omega$ external passive quenching resistor. The two fabricated SPADs were scanned at  $V_E = 1.5 \text{ V}$  and  $V_E = 2.5 \text{ V}$ . The data were reconstructed into 2D and 3D images, which are shown in Fig. 6. Through these results, it is possible to determine an exact dimension of the effective active area for each SPAD where the avalanche multiplication actually occurs. The drawn active area is 2.5  $\mu$ m in diameter, but in the case of the conventional SPAD, there is a slight contribution from the GR side, around 2.6  $\mu m$  in diameter at  $V_E=1.5$  V, and 2.9  $\mu m$  in diameter at  $V_E=2.5$  V based on the FWHM count of the LSM result. On the other hand, in the case of the DAR SPAD, it was confirmed that the effective active area is 3.68  $\mu m$  in diameter at  $V_E = 1.5$  V, and 4.44  $\mu$ m in diameter at  $V_E = 2.5$  V based on FWHM count of the

Fig. 9. Z-axis 2D cross-section of the LSM data.

LSM result. The results clearly demonstrate that the proposed GR optimization expands the avalanche multiplication region. The LSM experimental results also confirm the LET results, as the  $V_E$  increases the DAR SPAD exhibits a wider expansion region than the conventional SPAD. Based on the experimental results obtained from both the LET and LSM studies, the actual dimensions of the effective active area were used as 'SPAD active area' in (1) in calculating the PDP.

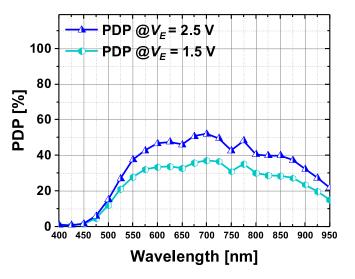

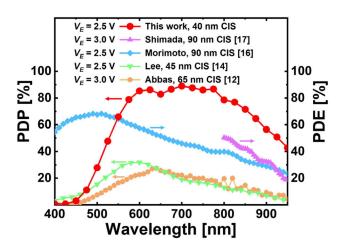

The PDP is determined experimentally by measuring the ratio of the number of electrical output pulses generated by the SPAD in response to the number of incident photons. The number of electrical output pulses generated by the SPAD can be measured by a high-performance oscilloscope and the number of incident photons can be calculated by the optical power incident to the SPAD using an integrating sphere and a ref. PD. PDP measurements were conducted in the range of wavelength from 400 nm to 950 nm, and the results are depicted in Figs. 7 and 8. Both conventional and DAR SPADs show low PDPs in the range of wavelength under 450 nm because the photon-generated electrons in the P-substrate cannot overcome the barrier of the other p-n junction between the P-substrate and DNW. As a result, carriers by incident photons with wavelengths between 400 nm and 450 nm at the surface of the SPAD rarely trigger avalanche multiplication. The main difference between conventional and DAR SPADs is their PDP performance beyond the wavelength of 450 nm. The conventional SPAD has a peak PDP of 52% at a wavelength of 700 nm and a PDP of 23% at a wavelength of 940 nm when  $V_E = 2.5$  V. While conventional SPAD also has good PDP performance, the proposed DAR SPAD, thanks to the wider multiplication region and carrier collection region achieved through optimized doping concentration at the GR, has achieved approximately twice as high in PDP. The DAR SPAD achieves a peak PDP of 89% at a wavelength of 700 nm and a PDP of 45% at a wavelength of 940 nm when  $V_E = 2.5$  V. The reason can be explained through the Z-axis 2D cross-section of the LSM data in Fig. 9. The incident optical power to both SPADs is the same but the result shows totally different shapes

Fig. 10. DCR results of both conventional and DAR SPADs at the various  $V_E$ .

and counts. The number of photon counts of the DAR SPAD is more than double that of the conventional SPAD in the entire avalanche multiplication region. Especially, the GR region of the DAR SPAD shows much higher counts thanks to the larger avalanche multiplication and carrier collection regions extended vertically and horizontally.

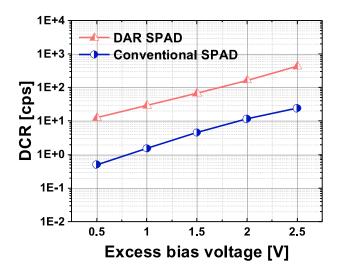

DCR was also characterized firstly at room temperature. DCR refers to the number of counts generated by the SPAD in the absence of any incident photon. The dark count can be triggered by several types of carriers such as thermally generated carriers, trapped carriers, and surface state of both P-substrate between the dielectric side and backside etching/thinning side from the BSI process. The results for both conventional and DAR SPADs are shown below 500 cps DCR at the  $V_E=2.5~\mathrm{V}$  as depicted in Fig. 10. The DCR is proportional to the multiplication region and carrier collection region which respectively contribute to the movement of carriers. The higher DCR of the DAR SPAD compared to the conventional SPAD can be attributed to its wider effective active area and carrier collection region. However, the SPAD exhibits sufficiently low DCR. Specifically, the DCR of DAR SPAD normalized by effective active area is about 27 cps/ $\mu$ m<sup>2</sup>. The main factor that can trigger dark count in SPADs fabricated using the BSI process is the presence of dangling bonds that remain after the backside thinning/etching process. However, both SPADs are isolated from the backside etched/thinned surface of the P-substrate by DNW, so the main contributors to increasing DCR are likely to be thermally generated carriers and trapped carriers. The sources of dark counts in the proposed SPAD can be estimated by measuring them at various temperature conditions.

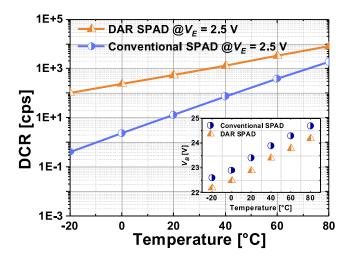

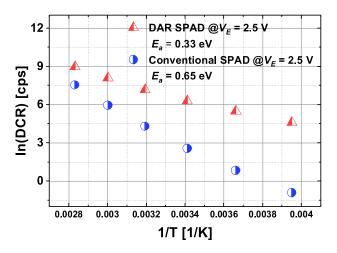

The DCR measurements were conducted at various temperatures in the range of  $-20 \sim 80$  °C in 20 °C increments with a temperature chamber. The results for both SPADs are shown in Fig. 11 as a function of temperature at  $V_E=2.5$  V. Through the temperature-dependent DCR measurement, several factors can be defined such as DCR variation with temperature, temperature coefficient, and activation energy ( $E_a$ ). The DAR SPAD exhibits a DCR of about 1.5 kcps/ $\mu$ m<sup>2</sup>, an acceptable rate even when the

Fig. 11. Temperature-dependent DCR results of both conventional and DAR SPADs at  $V_E=2.5~\rm V$  and the temperature-dependent  $V_B$  in the inset.

Fig. 12. Arrhenius plot of both conventional and DAR SPADs at  $V_E = 2.5 \text{ V}$ .

temperature reaches 80 °C. The conventional SPAD exhibits a DCR of about  $0.4 \text{ kcps/}\mu\text{m}^2$  which is lower than DAR SPAD due to its narrower effective active area and carrier collection region. The temperature coefficient is shown to be 15 mV/K as depicted in the inset of Fig. 11. This result confirms that DAR SPADs exhibit low changes in  $V_B$  and DCR with temperature. Thanks to these advantages, the proposed SPAD can be employed in various applications that require temperature-hardened devices. The activation energy is also extracted from the Arrhenius plot, depicted in Fig. 12. The  $E_a$  of the conventional SPAD has been calculated as 0.65 eV and the  $E_a$  of the DAR SPAD as 0.33 eVat  $V_E = 2.5$  V. The main contributor of the DCR can be the ion implantation of phosphorus, and it is estimated that the dominant noise mechanism of the DAR SPAD is trap-assisted tunneling while that of the conventional one is trap-assisted thermal generation.

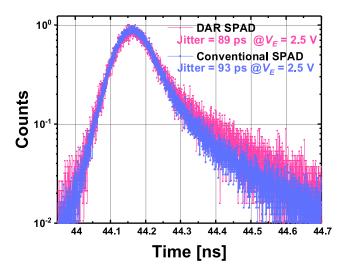

Fig. 13 shows the results of timing jitter measurements of both SPADs conducted when  $V_E = 2.5$  V at room temperature. Both the conventional and DAR SPADs were measured under the same conditions using a 940 nm picosecond pulsed laser as a light source and employing the time-correlated single-photon

Fig. 13. Timing jitter results of both conventional and DAR SPADs at  $V_E = 2.5 \ \mathrm{V}.$

Fig. 14. Inter-avalanche time histogram of the DAR SPAD at  $V_E=2.5~{

m V}$  along with a fitted exponential curve.

counting (TCSPC) technique with a high-speed oscilloscope. The period of the pulsed laser was carefully adjusted using a neutral density filter to prevent distortion of the jitter measurement. The timing jitter of the conventional SPAD is 93 ps at the FWHM, while that of the DAR SPAD is 89 ps at the FWHM. Considering the timing jitter of the SPADs, the spatial uncertainty in distance measurements can be estimated. The 89 ps timing jitter of the DAR SPAD results in a distance measurement uncertainty of approximately 13.3 mm and the spatial uncertainty of conventional SPAD is 13.9 mm. Both SPADs have similar FWHM values but the diffusion tail of the DAR SPAD is a little bit longer because its carrier collection region is wider than the conventional SPAD.

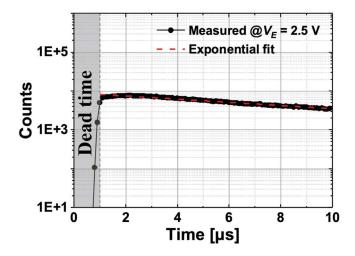

To evaluate the inter-avalanche time histogram of the DAR SPAD at  $V_E=2.5$  V, we used a 200 k $\Omega$  external passive quenching resistor. The result is depicted in Fig. 14, and the dead time is about 1  $\mu$ s. The result indicates afterpulsing probability at this dead time is negligible.

| Parameter                | Unit      | [10]            | [11]            | [12]              | [13]            | [14]              | [15]               | [16]                           | [17]                           | This work       |

|--------------------------|-----------|-----------------|-----------------|-------------------|-----------------|-------------------|--------------------|--------------------------------|--------------------------------|-----------------|

| Technology               | -         | 130 nm<br>CMOS  | 130 nm<br>CMOS  | 65 nm<br>CIS      | 65 nm<br>CIS    | 45 nm<br>CIS      | 140 nm<br>SOI CMOS | 90 nm<br>CISª                  | 90 nm<br>CISª                  | 40 nm<br>CIS    |

| Junction                 | -         | P+/N-well       | NLDD/PW         | PW/DNW            | PW/DNW          | P+/DNW            | P+/N-well          | n.a.                           | n.a.                           | P+/DNW          |

| Guard ring               | -         | PW              | NW              | Virtual<br>GR     | Virtual<br>GR   | PW                | PW                 | n.a.                           | n.a.                           | PW              |

| Shape                    | -         | Round           | Round           | Round             | Fermat          | Round             | Round              | n.a.                           | n.a.                           | Round           |

| Active area              | $\mu m^2$ | 28.3            | 28              | 27.6              | n.a.            | 122.7             | 113                | n.a.                           | n.a.                           | 15.47           |

| $V_B$                    | V         | 12.3            | 16.5            | 12                | n.a.            | 28.5              | 11.3               | 30                             | 22                             | 23.3            |

| $V_E$                    | V         | 4               | 1.5             | 3                 | 4.4             | 2.5               | 3                  | 2.5                            | 3                              | 2.5             |

| DCR                      | cps/µm²   | 265.3           | 1250            | 391.4             | 2463.1          | 55.4              | 396.1              | 0.044                          | $19^{\beta}$                   | 27              |

| Peak PDP<br>(Wavelength) | %         | 11<br>(@725 nm) | 13<br>(@700 nm) | 27.5<br>(@640 nm) | 29<br>(@660 nm) | 31.8<br>(@600 nm) | 26<br>(@500 nm)    | 69.4 <sup>7</sup><br>(@510 nm) | 50.5 <sup>δ</sup><br>(@800 nm) | 89<br>(@700 nm) |

| PDP<br>@905 nm           | %         | n.a.            | n.a.            | 9                 | 8               | 9                 | 8                  | 28.7γ                          | 31.9δ                          | 58              |

| PDP<br>@940 nm           | %         | n.a.            | n.a.            | 7.5               | 5.5             | 7                 | 6.5                | 24.4 <sup>7</sup>              | 20.58                          | 45              |

95

(@700 nm)

107.7

119

(@637 nm)

TABLE I

SUMMARY AND COMPARISON OF THE STATE-OF-THE-ART BACK-ILLUMINATED SPADS

$^{\alpha}with\ microlens,\ ^{\beta}cps/pix,\ ^{\gamma}PDE\ with\ microlens\ and\ pyramid\ surface,\ ^{\delta}PDE\ with\ microlens\ and\ light\ trapping$

205

(@773 nm)

505

(@750 nm)

n.a.

Fig. 15. PDP comparison of the state-of-the-art SPADs.

Timing jitter

(Wavelength)

ps

# IV. COMPARISON AND DISCUSSION

Fig. 15 shows the achieved PDP with the proposed SPAD in comparison to the state-of-the-art SPADs. As shown in this graph, [16] shows high photon detection efficiency (PDE) with the charge-focusing technique and light trapping engineering. Also, the PDE of [17] is as good as [16] at the NIR wavelength range due to the effect of the pyramid surface for diffraction at the backside surface of the SPAD along with the use of 7  $\mu$ m thick epi. Since a microlens is built on each of the SPADs, the PDE can be considered as PDP by assuming that their fill factors are 100% with the microlens. Thanks to the wide carrier collection region, high E-field, metal reflector, and ARC as well as the optimized backside process based on the advanced CIS

100

(@940 nm)

137

(@940 nm)

89

(@940 nm)

Fig. 16. Performance comparison of SPADs: PDP at 940 nm vs timing jitter.

technology, the proposed DAR SPAD shows higher PDP values in the NIR range, where LiDAR sensors and 3D imagers operate. In case we compare the efficiency the other way around, i.e., in terms of PDE rather than PDP, with assuming that a microlens will concentrate all the incident photons into the effective active area, the contribution of the carrier collection region should be excluded. Therefore it is expected that the maximum achievable PDE is 92% of the PDP, as the contribution of the carrier collection region outside the active area is about 8% which is estimated with the LSM result shown in Fig. 6.

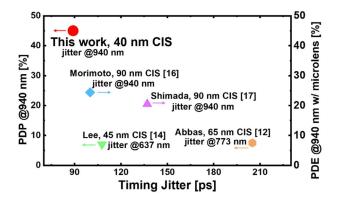

In addition, thanks to the wide and high E-field at the junction and the use of an isolated structure, it achieves superior timing jitter, which is the best performance of any BSI SPADs reported so far as shown in Fig. 16. The overall performance of the proposed SPAD is summarized in Table I, which also shows the comparisons with the state-of-the-art SPADs.

# V. CONCLUSION

We propose and demonstrate a DAR SPAD with GR-region doping optimization in 40 nm BSI CIS technology. Through the LET and LSM, the effective active area is clearly demonstrated, and the expansion of the avalanche multiplication region over the GR region is proved. The device is fully characterized, including PDP, temperature-dependent noise characteristics, and timing jitter. Thanks to the wide effective active area and carrier collection region, high E-field at the planar junction, optimized backside process, metal reflector, and ARC, the DAR SPAD achieves a DCR of 27 cps/ $\mu$ m², peak PDP of 89% at 700 nm, PDP of 45% at 940 nm, and timing jitter at 940 nm of 89 ps all at  $V_E=2.5$  V. The SPAD achieves, to the best of our knowledge, the highest PDP and the lowest timing jitter among reported BSI SPADs so far. We expect that the proposed SPAD can play a key role in various applications.

### ACKNOWLEDGMENT

The authors are grateful to SK hynix collaborators, especially Hyuk An, Suhyun Yi, Kyung-Do Kim, Jongchae Kim, Minseok Shin, Kwangjun Cho, Kwang June Sohn, Ji-Hoon Cho, Kangbong Seo, and Hoon-Sang Oh, for their help and support.

# REFERENCES

- C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 863–869, Jul./Aug. 2007.

- [2] J. A. Richardson, L. A. Grant, and R. K. Henderson, "Low dark count single-photon avalanche diode structure compatible with standard nanometer scale CMOS technology," *IEEE Photon. Technol. Lett.*, vol. 21, no. 14, pp. 1020–1022, Jul. 2009.

- [3] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2028–2035, Jul. 2011.

- [4] C. Veerappan and E. Charbon, "A substrate isolated CMOS SPAD enabling wide spectral response and low electrical crosstalk," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 299–305, Nov./Dec. 2014.

- [5] H. Xu, L. Pancheri, G.-F. D. Betta, and D. Stoppa, "Design and characterization of a p+/n-well SPAD array in 150nm CMOS process," *Opt. Exp.*, vol. 25, no. 11, pp. 12765–12778, May 2017.

[6] M. Sanzaro et al., "Single-photon avalanche diodes in a 0.16 μm BCD

- [6] M. Sanzaro et al., "Single-photon avalanche diodes in a 0.16 μm BCD technology with sharp timing response and red-enhanced sensitivity," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 2, Mar./Apr. 2018, Art. no. 3801209.

- [7] A. C. Ulku et al., "A 512 × 512 SPAD image sensor with integrated gating for widefield FLIM," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 1, Jan./Feb. 2019, Art. no. 6801212.

- [8] F. Gramuglia, M.-L. Wu, C. Bruschini, M.-J. Lee, and E. Charbon, "A low-noise CMOS SPAD pixel with 12.1 Ps SPTR and 3 ns dead time," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. no. 3800809.

- [9] F. Gramuglia et al., "Engineering breakdown probability profile for PDP and DCR optimization in a SPAD fabricated in a standard 55 nm BCD process," *IEEE J. Sel. Topics Quantum Electron.*, vol. 28, no. 2, Mar./Apr. 2022, Art. no. 3802410.

- [10] E. Charbon, M. Scandini, J. Mata Pavia, and M. wolf, "A dual backsideilluminated 800-cell multi-channel digital SiPM with 100 TDCs in 130 nm 3D IC technology," in *Proc. IEEE Nucl. Sci. Symp. Med. Imag. Conf.*, 2014, pp. 1–4.

- [11] J. M. Pavia, M. Scandini, S. Lindner, M. Wolf, and E. Charbon, "A 1 × 400 backside-illuminated SPAD sensor with 49.7 ps resolution, 30 pJ/sample TDCs fabricated in 3D CMOS technology for near-infrared optical tomography," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, pp. 2406–2418, Oct. 2015.

- [12] T. Al Abbas et al., "Backside illuminated SPAD image sensor with 7.83 µm pitch in 3D-stacked CMOS technology," in *Proc. IEEE Int. Electron Devices Meeting*, 2016, pp. 8.1.1–8.1.4.

- [13] S. Lindner et al., "A high-PDE, backside-illuminated SPAD in 65/40-nm 3D IC CMOS pixel with cascoded passive quenching and active recharge," *IEEE Electron Device Lett.*, vol. 38, no. 11, pp. 1547–1550, Nov. 2017.

- [14] M.-J. Lee et al., "High-performance back-illuminated three-dimensional stacked single-photon avalanche diode implemented in 45-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 24, no. 6, Nov./Dec. 2018, Art. no. 3801809.

- [15] M.-J. Lee, P. Sun, G. Pandraud, C. Bruschini, and E. Charbon, "First near-ultraviolet- and blue-enhanced backside-illuminated single-photon avalanche diode based on standard SOI CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 25, no. 5, Sep./Oct. 2019, Art. no. 3800206.

- [16] K. Morimoto et al., "3.2 megapixel 3D-stacked charge focusing SPAD for low-light imaging and depth sensing," in *Proc. IEEE Int. Electron Devices Meeting*, 2021, pp. 20.2.1–20.2.4.

- Meeting, 2021, pp. 20.2.1–20.2.4.

[17] S. Shimada et al., "A back illuminated 6μm SPAD pixel array with high PDE and timing jitter performance," in *Proc. IEEE Int. Electron Devices Meeting*, 2021, pp. 20.1.1–20.1.4.

- [18] A. R. Ximenes et al., "A 256 ×256 45/65nm 3D-stacked SPAD-based direct TOF image sensor for LiDAR application with optical polar modulation for up to 18.6dB interference suppression," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2018, pp. 96–98.

- [19] O. Kumagai et al., "7.3 A 189 × 600 back-illuminated stacked SPAD direct time-of-flight depth sensor for automotive LiDAR Systems," in *Proc. IEEE Int. Solid- State Circuits Conf.*, 2021, pp. 110–112.

- [20] I. Gyongy, N. A. W. Dutton, and R. K. Henderson, "Direct time-of-flight single-photon imaging," *IEEE Trans. Electron Devices*, vol. 69, no. 6, pp. 2794–2805, Jun. 2022.

- [21] M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, and S. Cova, "Progress in silicon single-photon avalanche diodes," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 852–862, Jul./Aug. 2007.

- [22] C. Y. Duh and J. L. Moll, "Electron drift velocity in avalanching silicon diodes," *IEEE Trans. Electron Devices*, vol. 14, no. 1, pp. 46–49, Jan. 1967.

- [23] C. B. Norris and J. F. Gibbons, "Measurement of high-field carrier drift velocities in silicon by a time-of-flight technique," *IEEE Trans. Electron Devices*, vol. 14, no. 1, pp. 38–43, Jan. 1967.

- [24] D. K. Schroder, "Carrier lifetime in silicon," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 160–170, Jan. 1997.

[25] S. Dutta et al., "The avalanche-mode superjunction LED," *IEEE Trans.*

- [25] S. Dutta et al., "The avalanche-mode superjunction LED," *IEEE Trans Electron Devices*, vol. 64, no. 4, pp. 1612–1618, Apr. 2017.

- [26] S. Dutta, G. J. M. Wienk, R. J. E. Gueting, J. Schmitz, and A.-J. Annema, "Optical power efficiency versus breakdown voltage of avalanche-mode silicon LEDs in CMOS," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 898–901, Jul. 2017.

- [27] V. Agarwal et al., "Data transmission capabilities of silicon avalanche mode light-emitting diodes," *IEEE Trans. Electron Devices*, vol. 65, no. 11, pp. 4883–4890, Nov. 2018.

Eunsung Park received the B.S. degree in electronic engineering from Gachon University, Gyeonggi-do, South Korea, in 2019. He is currently working toward the M.S. and Ph.D. degrees with Yonsei University, Seoul, South Korea. Since 2019, he has been a Student Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul. His research interests include single-photon detectors/sensors, Si-SPADs in CMOS, and CIS technologies.

**Doyoon Eom** received the B.S. degree in electrical and electronic engineering in 2020 from Yonsei University, Seoul, South Korea, where he is currently working toward the M.S. degree. Since 2021, he has been a Student Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul. His research focuses on single-photon avalanche diodes (SPADs) in CMOS technology.

Myeong-Hun Yu received the B.S. degree from the Department of Electronic and IT Media Engineering, Seoul National University of Science and Technology, Seoul, South Korea, in 2023. Since 2022, he has been an Internship Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul. His research interests include single-photon detectors/sensors, Si-SPADs, and SPAD-based detectors fabricated in CMOS and CIS technologies.

Yun-Mi Moon received the B.S. degree from the Department of Electronic and IT Media Engineering, Seoul National University of Science and Technology, Seoul, South Korea, in 2023. Since 2022, she has been an Internship Researcher with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul. Her research interests include single-photon avalanche diodes in CMOS, and applications of SPADS, CMOS Image Sensor, and LiDAR/ToF.

Dae-Hwan Ahn was born in Jeollabuk-do, Korea, on June 8, 1989. He received the B.S. degree in electric and electronic engineering from the University of Toyama, Toyama, Japan, in 2014, and the M.S. and Ph.D. degrees in electronic engineering from the University of Tokyo, Tokyo, Japan, in 2016 and 2019, respectively. He is currently a Postdoctoral with the Center for Opto-Electronic Materials and Devices, Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology, Seoul, South Korea. His research focuses on the technologies of advanced CMOS devices.

Jongtae Ahn received the B.S. and Ph.D. degrees from the Department of Physics, Yonsei University, Seoul, South Korea, in 2015 and 2020, respectively. Since 2020, he has been a Postdoctoral Researcher with the Korea Institute of Science and Technology, Seoul, South Korea. His research interests include fundamental and applied aspects of low dimension nanostructured semiconductors based electronic/optoelectronic devices.

**Do Kyung Hwang** received the B.S. and Ph.D. degrees in materials science & engineering and applied physics from Yonsei University, Seoul, South Korea, in 2008. From 2008 to 2009, he was a Postdoctoral Associate with the Korea Institute of Science and Technology (KIST). From 2009 to 2012, he was a Postdoctoral Fellow with the Georgia Institute of Science and Technology, Atlanta, GA, USA. He is currently a Principal Research Scientist with KIST and a Professor with the KU-KIST Graduate School of Converging Science and Technology. His

research interests include fundamental and applied aspects of organic/metal oxide semiconductors and low dimension nanostructured semiconductors based electronic/optoelectronic devices.

Woo-Young Choi (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1986, 1988, and 1994, respectively. His doctoral dissertation concerned the investigation of molecular-beam grown InGaAlAs laser diodes for fiber-optic applications. From 1994 to 1995, he was a Postdoctoral Research Fellow with NTT Opto-Electronics Laboratories, where he worked on femtosecond all-optical switching devices based on low-temperature grown

InGaAlAs quantum wells. In 1995, he joined the Department of Electrical and Electronic Engineering, Yonsei University, Seoul, South Korea, where he is currently a Professor. His research interests include high-speed electronic circuits, silicon photonics, and Si image sensors.

Myung-Jae Lee (Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical and electronic engineering from Yonsei University, Seoul, South Korea, in 2006, 2008, and 2013, respectively. His doctoral dissertation concerned silicon avalanche photodetectors fabricated with standard CMOS/BiCMOS technology. From 2013 to 2017, he was a Post-doctoral Researcher with the Faculty of Electrical Engineering, Delft University of Technology (TU Delft), Delft, The Netherlands, where he worked on single-photon sensors and applications based on

single-photon avalanche diodes. In 2017, he joined the School of Engineering, École Polytechnique Fédérale de Lausanne (EPFL), Neuchâtel, Switzerland, as a Scientist, working on advanced single-photon sensors/applications and coordinating/managing several research projects as a Co-Principal Investigator. Since 2019, he has been a Principal Investigator/Principal Research Scientist with the Post-Silicon Semiconductor Institute, Korea Institute of Science and Technology (KIST), Seoul, South Korea, where he has led the research and development of next-generation single-photon detectors and sensors for various applications. His research interests include photodiodes/photodetectors to single-photon detectors/sensors, concentrating since 2006 on CMOS-compatible avalanche photodetectors and single-photon avalanche diodes and applications thereof (e.g., LiDAR, ToF, 3D vision, biophotonics, quantum photonics, space, security, silicon photonics, and optical interconnects).