# 200Mbps Burst Mode Clock and Data Recovery

\* (a)

(a)

#### **Abstract**

A burst mode clock and data recovery circuit is realized that can operate in 200Mbps range. The circuit is capable of extracting clock signals from NRZ type burst-mode data packets and recover input data without missing any data. It also has a retiming block that reduces jitter noises. The circuit is fabricated in 3.3V, TSMC  $0.35\mu m$  CMOS technology and measurements are done that confirm the operation of the circuit.

1.

burst mode data 가 ATM-PON

burst mode

[1-2]. Clock and Data

Recovery(CDR) circuit 1

retiming

burst mode

CDR

MOSIS TSMC 0.35µm CMOS

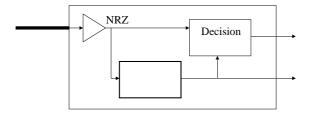

## 2. Clock and Data Recovery Circuit

CDR 2

. PLL

, jitter

S2P(serial to parallel)

[3].

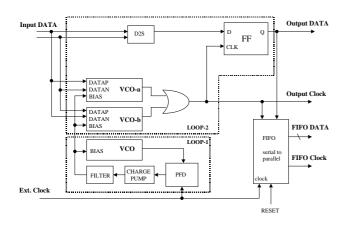

2 LOOP 1 PLL (Phase Locked Loop)

inverter chain VCO (Voltage Controlled Oscillator)

PFD (Phase frequency Detecter), filter

. LOOP 1

LOOP 2가

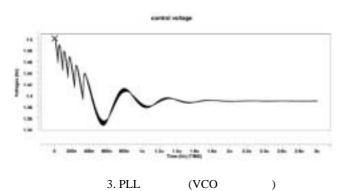

, 3

( 1.8µsec)

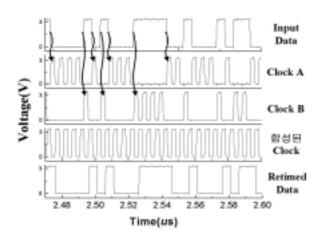

VCO-a VCO-b

A, Clock B

[3]. 2<sup>7</sup>-1 PRBS(Pseudo Random Binary

Sequences;  $2^7-1$ )

가

4 .

, PLL 200Mbps

.

## i Network Lab.

jitter 7†

7† , S2P

[4]. 8 25Mbps

S2P .

3.

CDR MOSIS TSMC  $0.35\mu m$  CMOS , package 48pin PTQFP . 5 layout 2.5mm  $\times$

## 1. Summary of CDR circuits

| Frequency                        | 160MHz - 240MHz     |

|----------------------------------|---------------------|

| Power supply                     | 3.3V single         |

| Power consumption(including I/O) | 350mW @ 200MHz      |

| Technology                       | 1P - 4M 0.35μm CMOS |

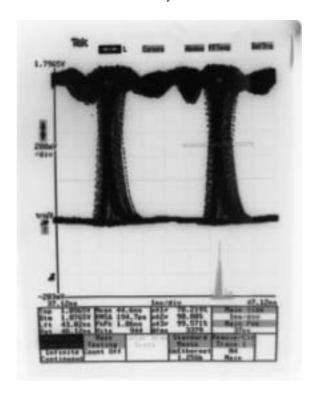

chip Anritsu MP1632A PPG

Tek. 11801C sampling Osc. eye

diagram

BER ( 6), Anritsu MP1632A ED

BER . 2<sup>23</sup>-1 PRBS input

data 7 .

4.

burst mode 0.35μm CMOS CDR . VCO

フト , burst mode フト , jitter S2P フト . フト

-- ,

[1] T. Kajiwara, E. Maekawa, *et al.*, "An optical receiver design for ATM-PON access system", 1996 Global Telecommunications Conference, Vol. 3, pp. 1613–1617.

[2] S.H. Ide, *et al.*, "+3.3V PON Receiver IC with a High-Speed ATC Circuit", 1997 EDMO, pp.141 –146.

[3] Y. Ota, *et al.*, "High-Speed, Burst-Mode, Packet-Capable Optical Receiver and Instantaneous Clock recovery for Optical bus Operation", Journal of Lightwave Technology, Vol.12, No.2, pp. 325–331, 1994.

[4] A.E. Dunlop *et al.* "150/30Mb/s CMOS Non-Oversampled Clock and Data Recovery Circuits with Instantaneous Locking and Jitter Rejection", 1995 Solid-State Circuits Conference, pp. 44–45.

# 1. Configuration of Clock and Data Recovery circuits

2. Clock and Data Recovery circuits

4. Clock and Data Recovery

5. Layout

6. Eye diagram