# 2008년도 **SoC** 학술대회

2008 SoC Conference

http://scc2008.sogang.ac.k

일 시: 2008년 5월 10일 (토) 9:00-18:00

장 소 : 서강대학교 마테오관

주 최 : 대한전자공학회 SoC 설계 연구회

주 관: 서강대학교

후 원: 마그마 코리아, KETI, 한국엔토, Synopsys, 휴인스, 리버트론, 나인플러스, IEEE CAS Seoul Chapter, IEEE SSCS Seoul Chapter

#### Session 5. 09:30 ~ 11:00

Room 20

# Signal Integrity and Interconnect Modelling/ SoC Design Methodology

좌장: 감교선 (인원대)

5.1 일본(어그러사僧 고라한 크로스톡 회미 방법

정시백(하이닉스), 박은석, 김주호(서강대)

5.2 이러 Power Distribution Networks에서 PLL의 지터 성능 분석

손영상, 위재경(숭실대)

# 5,3 지연을 최소화하기 위한 인터카넥트 모델링

윤진성, 최우양(연세대)

5.4 Application Specific On Ohip Network를 위한 Traffic Generator의Multi-Level Traffic Modeling 기법

하건석, 조성만, 송용호(한양대)

5,5 Novel Low-Complexity Feed-Sciomon Decoder

백재현, 선우명훈(서울대, 야구대)

5.6 Synopays Milyway Database환경에서 구현된 Post-layout Gate-Level Logic Smulator

김명진, 방성용, 정의양(언세대), 윤성로(고려대)

#### Session 6: 09:30 - 11:00

Poors 203

# Signal Integrity and Interconnect Modelling/ SoC Design Methodology

좌장 : 조경순 (한국외대)

6.1 2차원 바코드 인식을 위한 영상처리 기술

남현욱, 이월증, 정민식, 한종수, 김경관, 유훈(동서대)

6,2 H,264/JPEG 코덱을 위한 통합 변환 및 양자화 회로 설계

집준호, 천동업, 이산당, 조정순(한국의대)

6,3 관심 양약을 고려한 적용적 ME 탐색 기법

정성훈, 이채운, 이렇게(서울대)

6.4 SFT 알고리즘의 하드웨어 구현을 위한 리사이즈 모듈 설계

박찬일, 이수현, 정용진(광운대)

6.5 추정기도 영역 분형을 이용한 효율적인 음원 위치 추정 시스템 및 지능형 농기계 인전 시스템 적용

집용은, 홍선아, 정진군(전복대)

# 지연를 최소화하기 위한 인터커넥트 모델링

윤진성, 최우영 연세대학교 전기전자공학과

전화: (02)2123-7709, E-mail: polo4891@tera.yonsei.ac.kr

# Interconnect Modeling to Minimize Delay in VLSI Circuits

Jin-Sung Yoon and Woo-Young Choi

Department of Electrical and Electronic Engineering, Yonsei University

#### 요 약

본 논문에서는 VLSI 회로에서 지연을 최소화하기 위해 인터커넥션 라인을 모델링 하였다. 인터커넥션 라인에 존재하는 저항과 캐패시턴스, 인덕턴스 성분들을 수식과 EM 시뮬레이션으로 추출하여 모델링을 하였다. 인터커넥트 지연을 측정하기 위해서 6단 링 오실레이터에 모델링된 인터커넥션을 사용하여 시뮬레이션을 한 후, 제작하여 인터커넥트 지연을 최소화하는 방법을 연구하였다.

#### Abstract

In this paper, we model interconnection lines to minimize delay in VLSI circuits. We extract and model resistance, capacitance and inductance in interconnection lines using equations and EM (Electromagnetic) simulation. To measure interconnect delay effects, we simulate 6-stage ring oscillators using modeled interconnection. Then, we implement and measure ring oscillators.

Keywords: interconnection modeling, parasitic component, delay model

# I. 서 론

VLSI에서 클럭 신호 주파수가 증가하고, 회로가 복잡해짐에 따라서 인터커넥션 라인에 의한 지연은 점차중요해 지고 있다. 복잡한 회로에서 적절한 설계를 하기 위해서는, 좀 더 정확한 인터커넥션 라인 모델링과신호 전파특성이 요구되어 진다<sup>[4]</sup>. 일반적으로 인터커넥트는 저항과 캐패시턴스로 구성된 모델을 사용하지만, 신호의 상승시간이 빨라지고, 인터커넥션 라인의 길이가 길어지면서 인덕턴스가 포함된 모델링이 요구되고 있다<sup>[1]</sup>.

본 논문에서는 CMOS 0.18 / 1P6M 공정을 사용하여 인터커넥트에 존재하는 저항, 캐패시턴스와 인덕턴

스를 수식과 전자기 (EM) 시뮬레이션으로 추출하여 모델링을 하였다. 인터커넥트의 지연을 측정하기 위해 6단 링 오실레이터에 모델링된 다양한 인터커넥션 연 결을 넣어 제작 후 측정하여, 인터커넥션 라인에 의한 지연을 최소화하는 방법에 대해서 알아보았다.

#### Ⅱ. 본 론

#### 1. 인터커넥트 지연

회로에서 전체적인 로직 지연은 게이트 지연과 저항과 캐패시턴스에 의한 인터커넥트 지연의 합으로 정의되어진다<sup>[1]</sup>. 기존의 VLSI 설계에서는 부하 캐패시턴스에 의한 게이트 지연이 지배적이어서, 인터커넥트에 의

한 지연의 영향은 매우 적었다. 그러나 공정 기술이 발전하여 서브 마이크론 기술로 이동하면서, 게이트 고유의 지연은 점점 줄어들지만, 칩 내부의 연결 길이가 길어지고, 저항과 캐패시턴스의 증가로 인터커넥트에 의한 지연의 영향이 증가하였다.

일반적으로, 로직 회로에서 지연은 주로 3가지 캐패 시턴스 성분에 의해서 결정되어진다<sup>[1]</sup>.

- 1) 트랜지스터의 내부 기생 캐패시턴스

- 2) 인터커넥트 캐패시턴스

- 3) 팬 아웃 게이트의 인풋 캐패시턴스

그 중에 1)과 3)은 회로 구조에 의해서 결정되기 때문에, 인터커넥션 라인을 변화시키면 라인의 총 캐패시턴스가 달라져서 지연을 결정하는 변수로 작용하게 된다

본 논문에서는 인터커넥션 라인을 메탈 층과 라인의 너비를 변화 시키면서 모델링을 한 후, 인터커넥션 라 인에 의한 지연을 측정하였다.

#### 2. 인터커넥트 내부 성분과 모델링

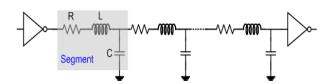

인터커넥션 라인은 그림 1 에서와 같이 저항, 캐패시 턴스와 인덕턴스로 이루어진 단위 블록의 연속으로 모 델링 된다.

단위 블록 당 저항, 캐패시턴스, 인덕턴스 값을 구하면 임의의 인터커넥션 라인을 모델링할 수 있게 된다.

그림 1. 인터커넥션 라인 모델

Fig. 1. Interconnection line model

# 가. 인터커넥트 내부 저항

인터커넥션 라인의 저항성분은 수식 (1)에 의해서 계산되어진다. 저항은 면적과 길이에 의하여 선형적으로 쉽게 계산되어진다. 인터커넥션 라인의 길이를 짧게 하고, 단면적을 넓게 해야 저항 성분을 줄일 수 있음을 알 수 있다.

$$R_{parasitic} = \rho * \frac{L}{A} \tag{1}$$

· ρ: 고유저항 [Ω-m]

· L: 인터커넥트의 길이

#### · A: 인터커넥트의 단면적 [너비(W)\*높이(H)]

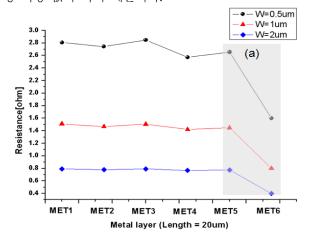

인터커넥트의 저항은 각 공정에서 주어지는 단위면 적당 저항 값 (Sheet resistance)을 계산하면 쉽게 계 산 할 수 있다. 인터커넥션 라인을 메탈의 층과 너비별 로 저항 값을 보면 그림 2와 같이 나타난다. (a) 영역에 서 저항 값이 작아지는 이유는 최상위 메탈은 단위면적 당 저항 값이 작기 때문이다.

그림 2. 메탈층과 너비에 따른 인터커넥션 저항

Fig. 2. Interconnect resistance versus metal layer and width

### 나. 인터커넥트 캐패시턴스

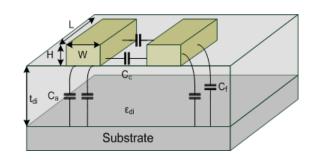

칩 내부에서는 인터커넥션 라인에 의해 그림 3과 같이 면적 캐패시턴스, 커플링 캐패시턴스, 플린징 캐패시턴스가 존재하게 된다. 본 논문의 모델링 과정에서는 하나의 인터커넥션 라인이 존재할 때를 모델링을 하였기 때문에 커플링 캐패시턴스는 계산과정에서 생략하였다.

면적 캐패시턴스와 커플링 캐패시턴스는 각각 수식 (2)와 (3)에 의하여 계산된다.

그림 3. 칩 내부에서 인터커넥트 캐패시턴스 Fig. 3. Interconnect capacitance in a chip

$$C_a = \frac{\varepsilon_{di}}{t_{di}} * W * L \tag{2}$$

$$C_f = \frac{2\pi * \varepsilon_{di}}{\log(t_{di}/H)} * L \tag{3}$$

· Ca: 면적 캐패시턴스 (Area capacitance)

· Cc: 커플링 캐패시턴스 (Coupling capacitance)

· Cf: 플린징 캐패시턴스 (Fringing capacitance)

·ε di: 유전상수 (Dielectric constant)

· tdi: 유전체 두께 (Dielectric thickness)

· L: 인터커넥트의 길이

· W: 인터커넥트의 너비

· H: 인터커넥트의 두께

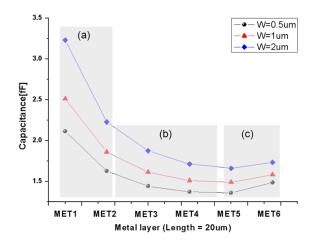

인터커넥트의 캐패시턴스는 메탈 층과 너비별로 그림 4와 같이 나타난다. 일반적으로 캐패시턴스는 메탈층이 위로 올라감에 따라 감소하는 경향을 가지고, 메탈의 너비가 증가함에 따라 증가하는 경향을 보인다.

영역별로 캐패시턴스가 변하는 이유는 다음과 같다.

(a) 영역: 유전율이 감소하고, 기판 (Substrate) 으로 부터 거리가 멀어지면서 캐패시턴스는 크 게 감소한다.

(b) 영역 : 메탈이 위로 올라감에 따라서 기판 (Substrate)으로부터 거리가 멀어짐에 따라서 면적 캐패시턴스가 감소한다.

(c) 영역 : 최상위 메탈은 두께가 두껍고, 그에 따른 플린징 캐패시턴스가 증가한다.

그림 4. 메탈층과 너비에 따른 인터커넥션 캐패시턴스 Fig. 4. Interconnect capacitance versus metal layer and width

#### 다. 인터커넥트 인덕턴스

인터커넥션 라인이 충분히 길어지게 되면 전송 선로 (Transmission Line)로 모델링이 된다. 따라서 인터커 넥트 내부의 인덕턴스 성분을 포함하여 모델링이 되어야 한다. 내부 인덕턴스는 전자기 시뮬레이션 (EM simulation)을 통해서 계산되었다.

길이가 250µm인 인터커넥션 라인에서 메탈 너비와 메탈 층에 따른 인덕턴스는 표 1과 같고, 이를 통해 단위면적당 약 1.1pH의 인덕턴스를 가짐을 알 수 있다.

표 1. 메탈 층과 너비에 따른 인터커넥션 인덕턴스 Table1. Interconnect inductance versus metal layer and width

|       | W=0.5 µm | $W=1\mu m$ | $W=2\mu m$ |

|-------|----------|------------|------------|

| MET 1 | 277      | 281        | 269        |

| MET 2 | 272      | 283        | 269        |

| MET 4 | 266      | 272        | 269        |

| MET 6 | 262      | 262        | 256        |

#### 3. 인터커넥트 지연 시뮬레이션

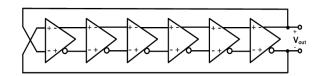

인터커넥트 지연을 측정하기 위하여 그림 5와 같이 6단 차동 링 타입 발진기로 시뮬레이션 하였다. 각 인 터커넥트의 메탈 층과 너비를 바꾸어 설계한 후, 각각 의 조건에 대하여 주파수를 측정하였다.

그림 5. 6단 차동 링 타입 발진기 Fig. 5. 6-stage ring type oscillator

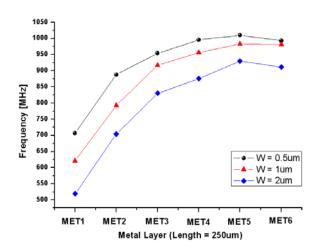

수식 (4)와 같은 관계에 따라 주파수로부터 지연의 영향을 파악할 수 있다. 시뮬레이션 결과는 그림 6과 같다.

$$\tau = \frac{1}{2 \cdot n \cdot f} \tag{4}$$

· f: 발진 주파수 (Oscillation frequency)

· n: 발진기 단수 (Oscillation stage)

· τ: 신호 전달지연 (Signal propagation delay)

오실레이터의 발진 주파수는 인터커넥트의 너비가 좁고, 상위 메탈을 사용할수록 증가함을 알 수 있다. 즉, 인터커넥트에 의한 지연을 줄이기 위해서는 너비를 가늘게 하고, 상위 메탈을 사용해야 함을 알 수 있다. 이와 같은 결과는 그림 4와 비교해 보았을 때 인터 커넥트의 지연은 캐패시턴스 성분에 의해 지배적으로 결정됨을 알 수 있다.

그림 6. 메탈층과 너비에 따른 발진 주파수 Fig. 6. Oscillation frequency versus metal layer and

width

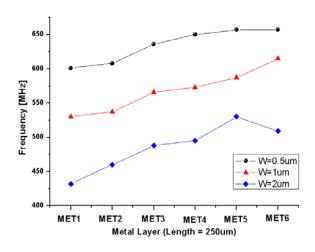

# Ⅲ. 실 험

오실레이터 발진주파수 측정은 Agilent E3633A Spectrum Anlayzer를 사용하였다. 측정된 발진 주파수는 그림 7과 같다. 발진 주파수가 인터커넥트의 너비가 감소하고, 상위 메탈을 사용할수록 증가함을 통해시뮬레이션과 경향성이 비슷함을 알 수 있다. 시뮬레이션과의 발진 주파수 오차는 인터커넥션의 커플링 캐패시턴스와 그 외 추가적인 링 오실레이터와 버퍼 등의기생성분들에 의해 나타난 것 이다.

그림 7. 인터커텍트 변화에 따른 발진 주파수 측정결과 Fig. 7. Oscillation frequency measurement result

## Ⅳ. 결 론

본 논문에서는 칩 내부에서의 인터커넥트에 의한 지연을 최소화 하는 방법을 연구하였다. 인터커넥션 라인을 저항과 캐패시턴스, 인덕턴스로 모델링을 한 후 메탈의 너비와 층을 바꾸어 가며 실험을 하였다. 인터커넥트에 의한 지연을 최소화하기 위하여 메탈 층은 상위층을 사용하고, 메탈의 너비는 얇게 하는 것이 좋다. 또한 인터커넥트의 길이가 길어지게 되면 전송 선로 (Transmission Line)로 모델링이 되어야 하기 때문에, 인덕턴스에 대한 고려가 필요하다.

#### 참 고 문 헌

- [1] S.M. Kang and Yusuf. Leblebici, "CMOS Digital Integrated Circuits, Analysis and Design, 3rd ed.," McGrawHill, pp.218~273 2005.

- [2] Narain D. Arora, Kartik V.Raol and Reinhard Schumann, "Modeling and Extraction of Interconnect Capacitance for Multilayer VLSI Circuits," *IEEE Trans. Computer-Aided Design,* Vol. 15, No. 1, pp58~67, January, 1996

- [3] Xiaoning. Qi, Bendik Kleveland, Zhiping Yu, Simon Wong, Robert Dutton, Tak Young, "On-chip Inductance Modeling of VLSI Interconnects," *IEEE Int. Solid-State Circuits Conf.* 2000. Dig. Tech. Papers, San Francisco, Jan. 2000, pp.172~173

- [4] Yehea I.Ismail, Eby G. Friedman, Jose L.Neves, "Equivalent Elmore delay for RLC Trees," *IEEE Trans. Computer-Aided Design*, Vol. 19, No. 1, pp83~97, January, 2000.