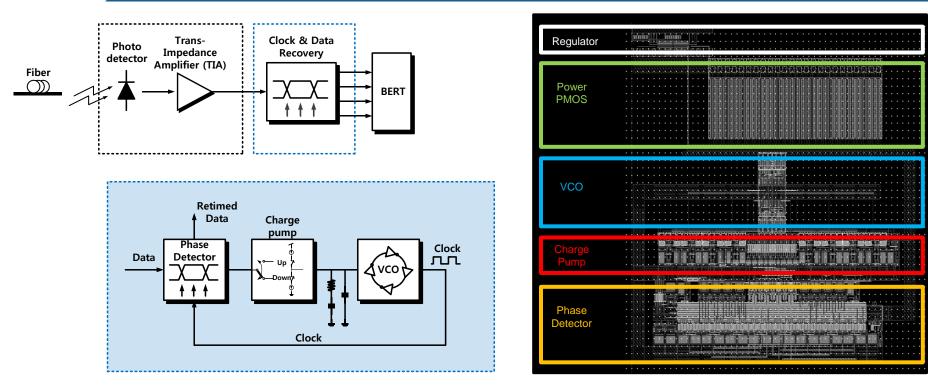

## **Designing high speed CDR for Optical Rx**

- Noisy and Asynchronous data → Clear & Synchronous data

- 20Gb/s quarter-rate CDR for optical Rx.

- Inductorless

- Deserializer

- High input sensitivity

- Ideal modeling of CDR

Clock align

**High-Speed Circuits and Systems Lab**

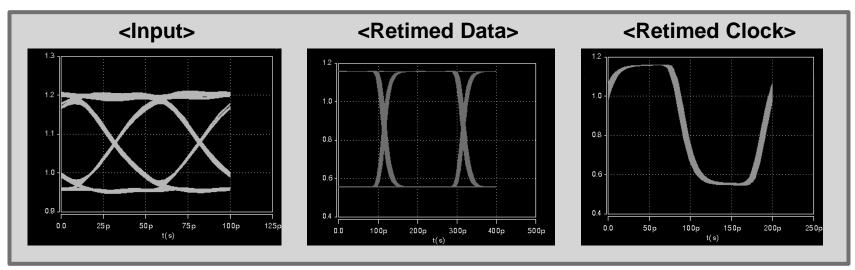

## **Designing high speed CDR for Optical Rx**

• Post-layout simulation

- 20Gb/s CDR → Retimed Data & Clock

- FF, NN, SS corner

- Future Work

- 20Gb/s Board design

- − Monitoring circuit for sensing & reacting  $\rightarrow$  Clock phase align

- PLL based dual loop CDR

- CDR with FD